|

||

| Products Download Events Support Videos | ||

Technical Support

On-Line Manuals

RL-ARM User's Guide (MDK v4)

Host Controller Driver Configuration

Host Controller Driver Configuration

The section explains the configuration options for the USB Host Controller Driver layer, which supports the Custom EHCI for NXP Devices, OHCI standard and the custom USB Host Controller Driver for the ST STM32F10x/20x/40x device series. The configuration options are set in driver module usbh_ehci_device family.c, usbh_ohci_device family.c or usbh_device family.c files.

Custom Enhanced Host Controller Interface for NXP Devices (Custom EHCI)

Custom Enhanced Host Controller Interface for NXP Devices (Cuatom EHCI) is activated by selecting Custom EHCI for NXP Devices Controller Interface in the usb_config.c file. Enable this option when using any device that supports Custom EHCI for NXP Devices.

The following configuration settings are available:

-

USBx Host EHCI Enable enables USB Host x controller. This

option corresponds x-th bit in #define USBH_EHCI_EN.

#define USBH_EHCI_EN 0x00000003 // both controllers enabled

-

USB Host EHCI Controller Base Address sets the EHCI memory

map base address. This option corresponds to #define

USBHx_EHCI_ADR.

#define USBH0_EHCI_ADR 0x40006000 // controller 0 base address #define USBH1_EHCI_ADR 0x40007000 // controller 1 base address

-

Root Hub ports used by EHCI Controller sets the active

root Hub ports used by the EHCI. This option corresponds to

#define USBHx_EHCI_PORTS.

#define USBH0_EHCI_PORTS 0x00000001 // controller 0 port 1 active #define USBH1_EHCI_PORTS 0x00000001 // controller 1 port 1 active

-

Size of memory used by EHCI sets the memory size used by

the communication data. The size of maximum 1048576 bytes can be

set. This option corresponds to #define

USBHx_EHCI_MEM_DATA_SZ.

#define USBH0_EHCI_MEM_DATA_SZ 4096 // memory size for USB0 data #define USBH1_EHCI_MEM_DATA_SZ 4096 // memory size for USB1 data

-

Maximum number of Queue Heads (Endpoints) used by EHCI

sets the maximum number of serviced endpoints. At least one

endpoint has to be set. Maximum 64 endpoints can be serviced.

This option corresponds to #define USBH_EHCI_NUM_qH.

#define USBH0_EHCI_NUM_qH 3 // 3 Endpoints for USB0 #define USBH1_EHCI_NUM_qH 3 // 3 Endpoints for USB1

-

Maximum number of Transfer Descriptors used by EHCI sets

the maximum number of transfer slots. At least one transfer slot

has to exist. A maximum of 64 transfer slots are possible. This

option corresponds to #define USBH_EHCI_NUM_qTD.

#define USBH0_EHCI_NUM_qTD 2 // 2 transfer slot for USB0 #define USBH1_EHCI_NUM_qTD 2 // 2 transfer slot for USB1

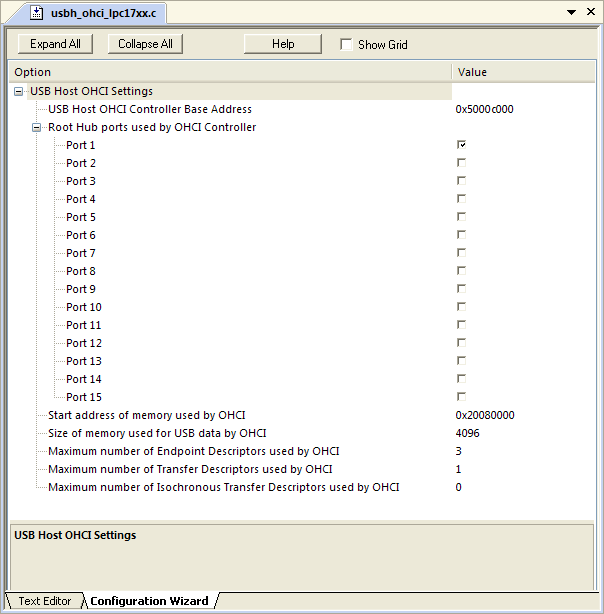

Open Host Controller Interface (OHCI)

Open Host Controller Interface (OHCI) is activated by selecting OHCI for Controller Interface in the usb_config.c file. Enable this option when using any device that supports OHCI.

The following configuration settings are available:

-

USB Host OHCI Controller Base Address sets the OHCI memory

map base address. This option corresponds to #define

USBH_OHCI_ADR.

#define USBH_OHCI_ADR 0x5000C000 // base address

-

Root Hub ports used by OHCI Controller sets the active

root Hub ports used by the OHCI. 15 Ports can be configured. This

option corresponds to #define USBH_OHCI_PORTS.

#define USBH_OHCI_PORTS 0x00000001 // activate the first port

-

Start address of memory used by OHCI sets the memory start

address for descriptors and communication data. This option

corresponds to #define USBH_OHCI_MEM_ADR.

#define USBH_OHCI_MEM_ADR 0x20080000 // memory address start

-

Size of memory used by OHCI sets the memory size used by

the communication data. The size of maximum 1048576 bytes can be

set. This option corresponds to #define

USBH_OHCI_MEM_DATA_SZ.

#define USBH_OHCI_MEM_DATA_SZ 4096 // memory size

-

Maximum number of Endpoint Descriptors used by OHCI sets

the maximum number of serviced endpoints. At least one endpoint

has to be set. Maximum 64 endpoints can be serviced. This option

corresponds to #define USBH_OHCI_NUM_ED.

#define USBH_OHCI_NUM_ED 3 // 3 Endpoints

-

Maximum number of Transfer Descriptors used by OHCI sets

the maximum number of transfer slots. At least one transfer slot

has to exist. A maximum of 64 transfer slots are possible. This

option corresponds to #define USBH_OHCI_NUM_TD.

#define USBH_OHCI_NUM_TD 1 // 1 transfer slot

-

Maximum number of Isochronous Transfer Descriptors used by

OHCI sets the maximum number of Isochronous transfer slots. A

maximum of 64 Isochronous transfers slots are possible. This

option can be set to zero. This option corresponds to #define

USBH_OHCI_NUM_ITD.

#define USBH_OHCI_NUM_ITD 0 // no Isochronous transfers

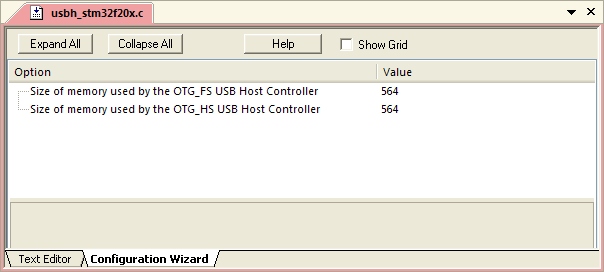

STM32F20x USB Host Controller

STM32F20x USB Host Controller is activated by selecting Custom for Controller Interface in the usb_config.c file. Enable this option when using any device that uses custom USB Host Controller.

The following configuration settings are available:

-

Size of memory used by the OTG_FS USB Host Controller sets

the memory size used by the OTG_FS communication data. The size

of maximum 1048576 bytes can be set. This option corresponds to

#define USBH0_STM32_SZ_MPOOL.

#define USBH0_STM32_SZ_MPOOL 564 // memory size for controller 0

-

Size of memory used by the OTG_HS USB Host Controller sets

the memory size used by the OTG_HS communication data. The size

of maximum 1048576 bytes can be set. This option corresponds to

#define USBH1_STM32_SZ_MPOOL.

#define USBH1_STM32_SZ_MPOOL 564 // memory size for controller 1

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |