|

||

| Products Download Events Support Videos | ||

Technical Support

On-Line Manuals

8051 Instruction Set Manual

Extended 8051 Memory Layout

The extended 8051 8051 architecture includes the following memory classes.

BIT, DATA, and IDATA

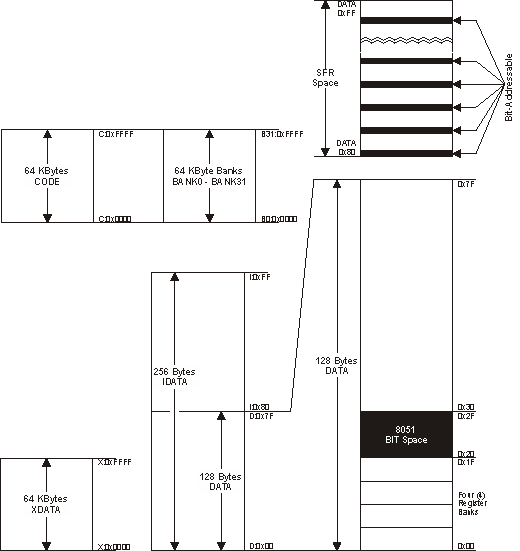

The BIT, DATA, and IDATA memory classes comprise the on-chip memory of the 8051 architecture and are shown in the following figure.

CODE, ECODE, and Memory Banks

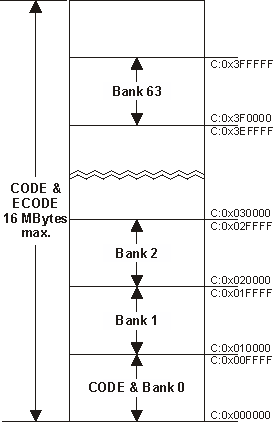

The CODE and ECODE

memory classes are typically stored in ROM that may be either

off-chip or on-chip. The CODE memory class may be used for

program code and refers to the first 64K (or Bank 0) of this

read-only memory area.

The CODE and ECODE

memory classes are typically stored in ROM that may be either

off-chip or on-chip. The CODE memory class may be used for

program code and refers to the first 64K (or Bank 0) of this

read-only memory area.

The ECODE memory class is used for constant variables declared

in code space above the first 64K of ROM.

In several variants the DPTR register is expanded to a 24-bit

register with an DPX SFR. For example, the Dallas/Maxim 390

provides new operating modes where this addressing is enabled. You

may even use the HCONST and HDATA memory classes with classic 8051

devices by using the memory banking available in LX51.

Bank 0 through Bank 63 allow your program to expand up

to 4 Mbytes when using memory banking.

XDATA and HDATA

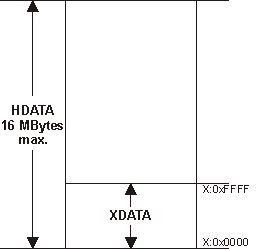

The XDATA memory class refers

to the first 64K of RAM which may be off-chip or on-chip.

The XDATA memory class refers

to the first 64K of RAM which may be off-chip or on-chip.

The HDATA memory class is used when RAM memory requirements

exceed 64K bytes. This memory class allows you to define up to 16

Mbytes of variable data.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |