|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC2136/01 — Pulse Width Modulator (PWM)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

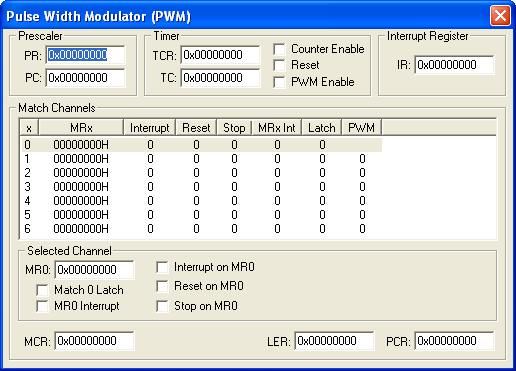

Pulse Width Modulator (PWM) Dialog

The Pulse Width Modulator dialog configures Pulse Width Modulator (PWM) simulation. When configured for PWM mode, the Timers (0 or 1) provide a basis for PWM outputs. Pulse period, pulse width, single and double edge controlled outputs are supported.

Prescaler

- PR (PWM Prescaler Register) contains the number of times (minus 1) PCLK must cycle before incrementing the PWM Timer Counter (TC).

- PC (PWM Prescaler Counter) contains the incrementing counter value. When this value equals the PR value plus 1, the PWM Timer Counter (TC) is incremented.

Timer

- TCR (PWM Timer Control Register) contains the Counter Enable, Counter Reset and the PWM Enable control bits.

- TC (PWM Timer Counter) contains the current value of the incrementing PWM Timer. When the Prescaler Counter (PC) reaches the Prescaler Register (PR) value plus 1, this counter is incremented.

- Counter Enable is set to enable the PWM Timer Counter and PWM Prescale Counter.

- Reset is set to reset the PWM Timer Counter and the PWM Prescale Counter to zero.

- PWM Enable enables PWM mode. In this mode, writing to a Match Register does not affect the the match result until a corresponding bit in Latch Enable Register (LER) is set followed by a PWM Match event.

Interrupt Register

- IR (Interrupt Register) contains the interrupt flags for PWM Match Channels 0-6. An interrupt flag is set when an interrupt occurs for that channel (MRx Interrupt).

Match Channels The Match Channel group allows simulation of 6 single-edge controlled or 3 double-edge controlled PWM outputs. You may modify the seven Match Channels to configure these PWM outputs to suit your requirements. Selected Channel

- MRx (Match Register x) contains the value to be compared to the Timer Counter (TC) value. When equal, a Match event occurs.

- Match x Latch is set to allow the last value written to a Match Register x to become active on the next timer reset.

- MRx Interrupt (Match Register x Interrupt) is set when a interrupt occurs for Match Channel 0-6

- Interrupt on MRx is set to allow an interrupt to occur on Match Channel 0-6 when Match Register x (MRx) equals the Timer Counter (TC) value.

- Reset on MRx is set to reset the Timer Counter (TC) when the Match Register (MRx) equals the Timer Counter (TC) value.

- Stop on MRx is set to stop the Timer Counter (TC) and Prescaler Register (PC) when the Match Register (MRx) equals the Timer Counter (TC) value. This condition also sets the Timer Counter Register (TCR) to zero.

- MCR (PWM Match Control Register) contains the Interrupt, Reset and Stop bits that control the selected Match Channel.

- LER (Latch Enable Register) contains the Match x Latch bits for each Match Channel.

- PCR (PWM Control Register) contains the bits that enable PWM outputs 0-6 and select single-edge or double-edge control for each output.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |