|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Texas Instruments LM3S8730 — Nested Vectored Interrupt Controller (NVIC)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

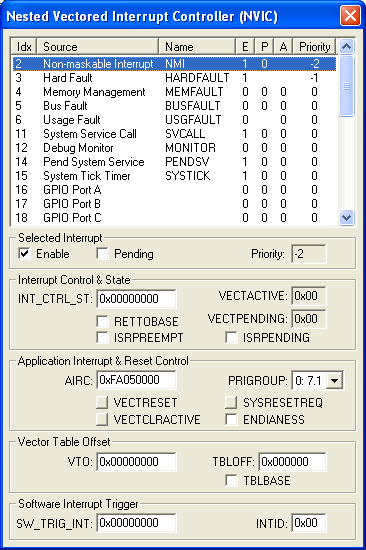

Nested Vectored Interrupt Controller (NVIC) Dialog

The Nested Vectored Interrupt Controller Dialog displays the status of all simulated MCU interrupts. The channel, source, name, vector, priority and interrupt state for each interrupt is displayed. You may select and configure each interrupt using the following control groups:

Selected Interrupt

- Enable is checked when this interrupt is enabled. You may manually enable the interrupt by setting this bit.

- Pending is checked when this interrupt occurred but has not been serviced. You may manually trigger the interrupt by setting this bit.

- Priority displays the priority assigned to the selected interrupt.

Interrupt Control & State

- INT_CTRL_ST (Interrupt Control & State Register) contains the following bit settings:

- RETTOBASE indicates that the current active interrupt is the only active interrupt.

- ISRPREEMPT indicates that the next pending interrupt becomes active.

- VECTACTIVE the interrupt number of the vector that is active.

- VECTPENDING the number of the pending interrupt (read only).

- ISRPENDING indicates that an interrupt is pending (read only).

Application Interrupt & Reset Control

- AIRC (Application Interrupt/Reset Control Register) contains the following bit settings:

- VECTRESET resets the system except for the debug components.

- VECTCLRACTIVE clears state information.

- SYSRESETREQ causes the external signal for reset to be raised.

- ENDIANESS selects the significant byte order of a word.

- PRIGROUP is used to divide the priority into group priority and subgroup priority.

Vector Table Offset

- VTO (Vector Table Offset Register) contains the vector table settings.

- TBLOFF contains offset of the vector table from Code or RAM.

- TBLBASE indicates if the table is in Code or RAM.

Software Interrupt Trigger

- SW_TRIG_INT (Software Trigger Interrupt Register) contains the following:

- INTID the indicated interrupt is pending.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |