|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Infineon XC164GM-8F — Asynchronous/Synchronous Serial Interface ASC0

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

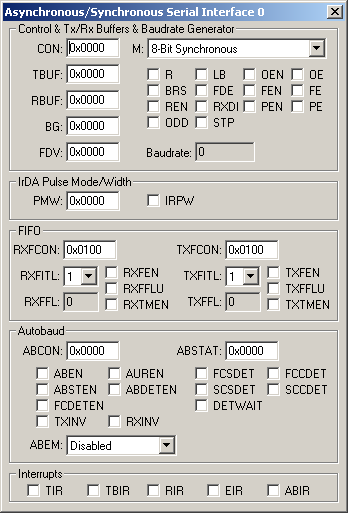

Asynchronous/Synchronous Serial Interface 0 Dialog

The Asynchronous/Synchronous Serial Interface 0 dialog displays and allows you to edit the configuration of the Asynchronous/Synchronous Serial Interface. The controls in this dialog are separated into several logical groups.

Control & Tx/Rx Buffers & Baudrate Generator

- CON (Control Register) contains the following control bits:

- M (Mode Control) displays and allows you to change the serial interface mode of operation (data length and synchronous or asynchronous).

- R (Baudrate Generator Run Control Bit) enables the baudrate generator.

- BRS (Baudrate Selection) is set to configure the prescale divisor to 3. If reset, the prescale divisor is configured to 2.

- REN (Receive Enable) enables serial data reception.

- ODD (Parity Selection) is set for odd parity.

- LB (Loopback Mode Enabled) enables loopback mode.

- FDE (Fractional Divider Enable) is set to use the fractional divider as a prescaler to generate the baudrate.

- RXDI (RxDI Invert in IrDA Mode) is set to invert received data.

- STP (Number of Stop Bits Selection) is set for 2 stop bits and reset for 1 stop bit.

- OEN (Overrun Check Enable) is set to check for data overrun or underflow.

- FEN (Framing Check Enable) is set to test for framing errors.

- PEN (Parity Check Enable) is set to enable parity checking.

- OE (Overrun Error Flag) indicates an overrun error was detected.

- FE (Framing Error Flag) indicates a framing error was detected.

- PE (Parity Error Flag) indicates a parity error was detected.

- TBUF (Transmit Buffer Register) contains the data to be transmitted.

- RBUF (Receive Buffer Register) contains the received data.

- BG (Baudrate Timer/Reload Register) contains the 13-bit reload value for the baudrate timer.

- FDV (Fractional Divider Register) contains the 9-bit fractional divider ratio value.

- Baudrate is the actual baudrate.

IrDA Pulse Mode/Width

- PMW (IrDA Pulse Width Value) contains an 8-bit value used to adjust the width on an IrDA pulse.

- IRPW (IrDA Pulse Width Selection) is set to use the PMW value for the IrDA pulse width. If reset, the IrDA Pulse Width is 3/16 bit time.

FIFO

- RXFCON (Receive FIFO Control Register) contains the RXFITL, RXFEN, RXFFLU and RXTMEN bit settings.

- RXFITL (Receive FIFO Interrupt Trigger Level) selects the number of bytes received before a receive interrupt request is generated.

- RXFFL (Receive FIFO Filling Level) contains the number of bytes in the receive FIFO.

- RXFEN (Receive FIFO Enable) is set to enable the Receive FIFO.

- RXFFLU (Receive FIFO Flush) is set to empty the Receive FIFO.

- RXTMEN (Receive FIFO Transparent Mode Enable) is set to enable Transparent mode. In this mode, during reception, the controller generates receive interrupts anytime data is available in the receive FIFO.

- TXFCON (Transmit FIFO Control Register) contains the TXFITL, TXFEN, TXFFLU and TXTMEN bit settings.

- TXFITL (Transmit FIFO Interrupt Trigger Level) selects the number of bytes transmitted before a transmit interrupt request is generated.

- TXFFFL (Transmit FIFO Filling Level) contains the number of bytes in the transmit FIFO.

- TXFEN (Transmit FIFO Enable) is set to enable the Transmit FIFO.

- TXFFLU (Transmit FIFO Flush) is set to empty the Transmit FIFO.

- TXTMEN (Transmit FIFO Transparent Mode Enable) is set to enable Transparent mode. In this mode, during transmission, the controller generates transmit interrupts after each data byte is stored and the transmit FIFO is not full.

Autobaud

- ABCON (Autobaud Control Register) contains the following control bit settings:

- ABEN (Autobaud Detection Enable) is set to enable auto baudrate detection.

- ABSTEN (Start of Autobaud Detection Interrupt Enable) is set to enable the autobaud detection interrupt.

- FCDETEN (First Character of Two-Byte Frame Detected Enable) is set to trigger an autobaud detection interrupt after the first and second bytes are detected within a two-byte frame.

- TXINV (Transmit Inverter Enable) enables the transmit inverter controlling echo mode and autobaud detection.

- AUREN (Automatic Autobaud Control of CON.REN) is set to enable the receiver (CON.REN) after the baudrate is successfully detected.

- ABDETEN (Autobaud Detection Interrupt Enable) is set to enable the autobaud detection interrupt.

- RXINV (Receive Inverter Enable) enables the receive inverter controlling echo mode and autobaud detection.

- ABSTAT (Autobaud Status Register) contains the following control bit settings:

- FCSDET (First Character with Small Letter Detected) is set when an ASCII "a" character is detected.

- SCSDET (Second Character with Small Letter Detected) is set when an ASCII "t" character is detected.

- DETWAIT (Autobaud Detection is Waiting)

- FCCDET (First Character with Capital Letter Detected) is set when an ASCII "A" character is detected.

- SCCDET (Second Character with Capital Letter Detected) is set when an ASCII "T" character is detected.

- ABEM (Autobaud Echo Mode Enable) can be set to enable echo mode always or just during autobaud detection.

Interrupts

- TIR (Transmit Interrupt) is set when the last bit of an asynchronous frame is transmitted.

- TBIR (Transmit Buffer Interrupt) is set when a character is moved from the transmit buffer(TBUF) to the transmit shift register.

- RIR (Receive Interrupt) is set when a received character frame is moved to the receive buffer(RBUF).

- EIR (Error Interrupt) is set when an error occurs on the serial channel.

- ABIR (Autobaud Interrupt) is set when an autobaud detection occurred.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |