|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Cadence Design Systems Inc. R8051XC (2 DPTR) — Arithmetic Unit

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

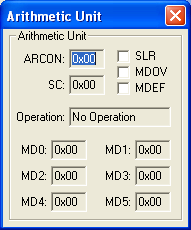

Arithmetic Unit Dialog

The Arithmetic Unit performs high-speed multiply, divide, bit shift and normalize operations using an integrated MDU in the processor core.

Arithmetic Unit Group

- ARCON (Control Register) contains the following control bits:

- SC (Shift Count) contains the number of shifts the MDU is to perform. SC is set to zero to perform floating-point normalization on the value in MD0-MD3.

- SLR (Shift Direction Bit) is set for right shift operation and reset for left shift operations.

- MDOV (Overflow Flag) is set if the result from a multiply is greater than 0xFFFF, or if division by zero, or if MD3.7 is set at the start of normalization.

- MDEF (Error Flag) is set if an arithmetic operation was interrupted by a new arithmetic operation. The register values are not valid when this condition occurs.

- Operation displays the type of operation performed by the MDU. The order in which the MD0-MD5 registers are written and read determines the operation type.

- MD0-MD5 (MDU Data Registers 0-5) holds the operand values for the requested arithmetic function and the resulting values after performing the requested function.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |