|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC11D14/302 — SSP Interfaces 0-1

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

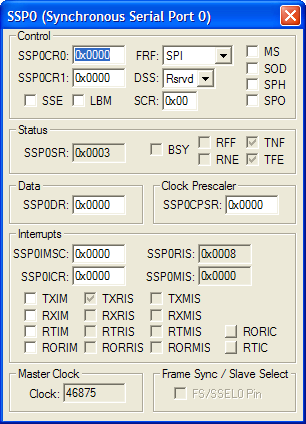

Synchronous Serial Peripheral 0 Dialog

The Synchronous Serial Port dialog displays and allows you to edit the configuration of the Synchronous Serial Ports. The controls in this dialog are separated into several logical groups.

Control

- SSPnCR0 (SSPn Control Register 0) contains the SSP control register 0 settings.

- SSPnCR1 (SSPn Control Register 1) contains the SSP control register 1 settings.

- SSE (SSP Enable) is set to enable the Synchronous Serial Port.

- LBM (Loop Back Mode Control) is set to connect received input to transmitted output.

- FRF (Frame Format) selects SPI, TI ot Microwire frameing format.

- DSS (Data Size Selection) selects the transfer data widths from 4-bits to 16-bits.

- SCR (Serial Clock Rate) is the number of prescaler output clocks per bit, minus 1.

- MS (Master/Slave Mode) is set to generate shift clocking from SCLK.

- SOD (Slave Output Disable) is set to prevent the SP controller from transmitting data.

- SPH (Clock Out Phase Control) is set to latch receive data on the leading clock edge and shift on the trailing edge. If reset, Shift receive data on the leading clock edge and latch on the trailing edge.

- SPO (Clock Out Polarity Control) is set make the clock line low-active and the leading clock edge is a high-to-low transition.

Status

- BSY (Busy Flag) indicates data transfer is in progress.

- RFF (Receive FIFO Full Flag) indicates the receive FIFO is full.

- RNE (Receive FIFO Not Empty Flag) indicates the receive FIFO contains unread data.

- TNF (Transmit FIFO Not Full Flag) indicates the transmit FIFO can accept data.

- TFE (Transmit FIFO Empty Flag) indicates that all data previously sent has been transmitted.

Data

- SSPnDR (SSPn Data Register) contains data to be sent or received.

Clock Prescaler

- SSPnCPSR (SSPn Clock Prescale Register) contains the PCLK divisor value (2-254) used to generate the prescaler output clock.

Interrupts

- SSPnIMSC (SSPn Interrupt Mask Set/Clear Register) contains the bits that enable the following four interrupts in the SSP controller:

- TXIM (Transmit Interrupt) is set to trigger an interrupt when the transmit FIFO is at least half empty.

- RXIM (Receive Interrupt) is set to trigger an interrupt when the receive FIFO is at least half full.

- RTIM (Receive Timeout Interrupt) is set to trigger an interrupt when the receive FIFO is not empty and nothing has been read for a predetermined time.

- RORIM (Receive Overrun Interrupt) is set to trigger an interrupt when the receive FIFO is full and another frame is received.

- SSPnRIS (SSPn Raw Interrupt Status Register) contains the SSP control register 0 settings.

- TXRIS (Raw Transmit Interrupt) is set to trigger an interrupt when the transmit FIFO is at least half empty.

- RXRIS (Raw Receive Interrupt) is set to trigger an interrupt when the receive FIFO is at least half full.

- RTRIS (Raw Receive Timeout Interrupt) is set to trigger an interrupt when the receive FIFO is not empty and nothing has been read for a predetermined time.

- RORRIS (Raw Receive Overrun Interrupt) is set to trigger an interrupt when the receive FIFO is full and another frame is received.

- SSPnMIS (SSPn Masked Interrupt Status Register) contains the following SSP masked interrupts:

- TXMIS (Masked Transmit Interrupt) is set to trigger an interrupt when the transmit FIFO is at least half empty.

- RXMIS (Masked Receive Interrupt) is set to trigger an interrupt when the receive FIFO is at least half full.

- RTMIS (Masked Receive Timeout Interrupt) is set to trigger an interrupt when the receive FIFO is not empty and nothing has been read for a predetermined time.

- RORMIS (Masked Receive Overrun Interrupt) is set to trigger an interrupt when the receive FIFO is full and another frame is received.

- SSPnICR (SSPn Interrupt Clear Register) is used by software to clear SSP interrupt conditions.

- RORIC (Receive Overrun Interrupt Clear) clears a Receive Overrun interrupt.

- RTIC (Receive Timeout Interrupt Clear) clears a Receive Timeout interrupt.

Master Clock

- Clock The SSP clock rate.

Frame Sync/Slave Select

- FS/SSELn pin Displays the status of the Frame Sync/Slave Select signal.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |