|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC1113/202 — System Control and Configuration

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

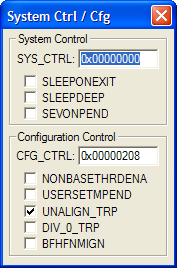

System Ctrl/Cfg Dialog

The System Control and Configuration Dialog displays and configures the system sleep and other options relevent to the Cortex core peripherals. You may select and configure each interrupt using the following control groups:

SYS_CTRL

- SLEEPONEXIT returns the processor to sleep mode or deep sleep mode when it completes execution of an exception handler.

- SLEEPDEEP is set to select deep sleep, rather than sleep on return from an exception.

- SEVONPEND (Send Event on Pending) if set, allows disabled interrupts to wake up the processor. If reset, only enabled interrupts or events can wake the processor.

CFG_CTRL

- NONBASETHRDENA if set, allows the processor to enter Thread mode from any exception return. If reset, the processor can only enter Thread mode when no exception is active.

- USERSETMPEND enables unprivileged software access to the Software Trigger Interrupt Register(STIR).

- UNALIGN_TRP enables unaligned access traps.

- DIV_0_TRP enables faulting or halting when the processor executes an SDIV or UDIV instruction with a divisor of 0.

- BFHFNMIGN (Bus Fault, Hard Fault, NMI Ingore) if set, data bus faults caused by load and store instructions are ignored.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |