|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Nuvoton NUC501ADN — GPIO (32-Bits)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

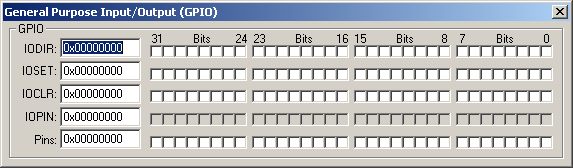

General Purpose Input/Output Dialog

The General Purpose Input/Output (GPIO) Dialog controls the direction of the general purpose port pins. You may use the following controls to select and configure the external interrupt settings.

GPIO Group

- IODIR (Input Output Direction Register) contains the direction assignments for each I/O port bit. The checkboxes are checked for output and unchecked for input.

- IOSET (Input Output Set Register) bits are checked to force a high level for a that port bit during output.

- IOCLR (Input Output Clear Register) bits are checked to force a low level for a that port bit during output.

- IOPIN (Input Output Pin Value Register) contains the current condition of the GPIO pins.

- Pins is used to manually control a pin value.

PORT VTREG

Data Type: unsigned long

The PORT VTREGs represent the I/O pins of the simulated MCU Port. You may read PORT to determine the state of the output pins. For example, in the command window you may type,

PORT

to obtain the value corresponding to the set pins of the port. You may also change the input values of port pins by changing the value of the VTREG. For example,

PORT=0x000000F0

sets the upper four port pins to a value of 1 and all other port pins to a value of 0. You may use the bitwise operators AND(&), OR(|) and XOR(^) to change individual bits of the PORT VTREGs. For example:

PORT |= 0x00000001; /* Set P0 Pin */ PORT &= ~0x00000200; /* Clr P9 Pin */ PORT ^= 0x00800000; /* Toggle P23 Pin */

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |