|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC1114/201 — Clocking & Power Control

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

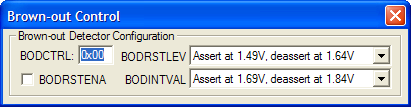

Brown-out Control Dialog

The Brown-out Control Dialog configures the brown-out detector of the device. With this dialog, you can choose the level of monitoring of brown-out events.

Brown-out Detector Configuration

- BODCTRL (Brown-out Control Register) contains the Brown-out configuration bit settings.

- BODRSTENA (Brown-out Reset Enable) when set, resets the device when a brown-out condition is detected.

- BODINTVAL (Brown-out Interrupt Assertion Level) sets brown-out assertion and de-assertion to 2.29/2.44 if set, or 1.69/1.84 if reset.

- BODRSTLEV (Brown-out Reset Level) is a fixed setting for reset assertion at 1.49V and reset de-assertion at 1.64V.

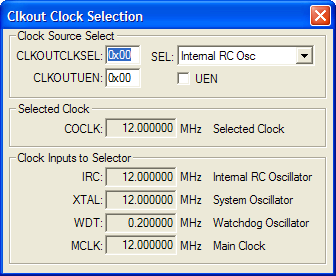

Clkout Clock Selection Dialog

The Clkout Clock Selection dialog selects the source of the input clocking from the 3 independent oscillators.

Clock Source Select

- CLKOUTCLKSEL (Clock Output Clock Select Register) configures the clkout_clk signal to be output on the CLKOUT pin.

- CLKOUTUEN (CLKOUT Source Update Enable Register) holds the update clock source enable bit setting.

- UEN checkbox sets or resets the update clock source enable bit.

Selected Clock

- COCLK displays the selected clock output value.

Clock Inputs to Selector

- Oscillators IRC, XTAL, WDT and MCLK display the frequency of each clock source.

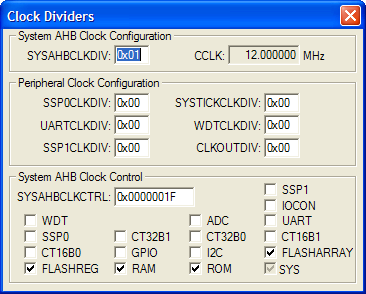

Clock Dividers Dialog

The Clock Dividers dialog displays the registers and settings for the CPU, USB and Peripheral clock supported by this device.

System AHB Clock Configuration

- SYSAHBCLKDIV (System AHB Clock Configuration Register) contains the 8-bit divisor used to create the CCLK signal from the PLL output.

- CCLK is the resulting Core Clock value.

USB Clock Configuration

- USBCLKDIV (USB Clock Configuration Register) contains the 4-bit divisor used to create the USBCLK signal.

- USBCLK is the resulting USB Clock value.

Peripheral Clock Configuration

- SSPCLKDIV (SSP Clock Divisor Register) contains the 4-bit divisor used to create the SSPCLK signal.

- UARTCLKDIV (UART Clock Divisor Register) contains the 4-bit divisor used to create the UARTCLK signal.

- TRACECLKDIV (TRACE Clock Divisor Register) contains the 4-bit divisor used to create the TRACECLK signal.

- SYSTICKCLKDIV (SYSTICK Clock Divisor Register) contains the 4-bit divisor used to create the SYSTICKCLK signal.

- WDTCLKDIV (WDT Clock Divisor Register) contains the 4-bit divisor used to create the WDTCLK signal.

- CLKOUTDIV (Clock Out Divisor Register) contains the 4-bit divisor used to create the CLKOUT signal.

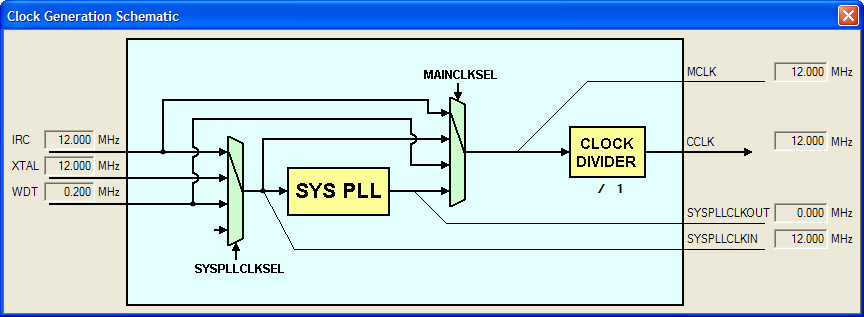

Clock Generation Schematic Dialog

The Clock Generation Schematic displays input clock values and the resulting generated clock values to be used by the application.

Clock generation Schematic

- IRC is the on-chip 12 MHz oscillator.

- XTAL is the value of the external crystal.

- WDT is the watchdog timer source clock value.

- MCLK is the generated main clock.

- CCLK is the generated core clock.

- SYSPLLCLKOUT is the resulting system PLL clock.

- SYSPLLCLKIN is the input clock for the system PLL.

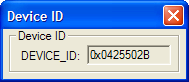

Device ID Dialog

The Device ID dialog displays the device ID for the target device.

Device ID

- DEVICE_ID is a read-only register that contains the device ID for each LPC11xx part.

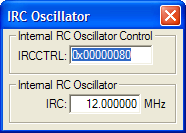

Internal RC Oscillator Dialog

The IRC Oscillator Control Dialog configures the internal resonant crystal (RC) control register of the device.

Internal RC Oscillator Control

- IRCCTRL (Internal RC Oscillator Control Register) contains the factory-preset IRC trim value.

Internal RC Oscillator

- IRC contains the internal RC oscillator value in MHz.

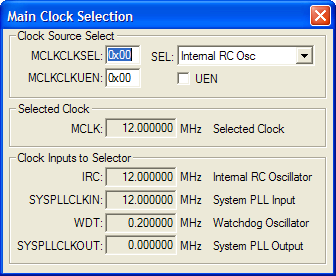

Main Clock Selection Dialog

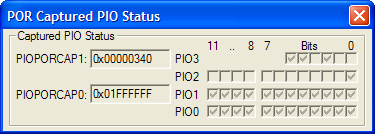

POR Captured PIO Status Dialog

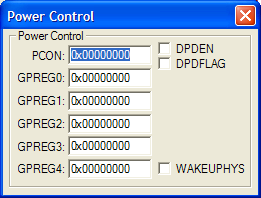

Power Control Dialog

The Power Control Dialog controls the power saving mode of the ARM controller. With this dialog, you can selectively enable or disable unused peripherals to save power.

Power Control

- PCON (Power Control Register) contains the DPDEN and DPDFLAG bits.

- DPDEN (Deep Power-down Mode Enable) enables deep power-down mode when an ARM/Cortex-M0 WFI/WFE instruction is executed.

- DPDFLAG (Deep Power-down Mode Flag) if set, indicates the device is in deep power-down mode.

- GPREGn (General Purpose Register n) colds data retained during deep power-down mode. GPREG4 hold the WAKEUPHYS setting.

- WAKEUPHYS (WAKEUP Pin Hysteresis Enable) if set, enables hysteresis for the WAKEUP pin.

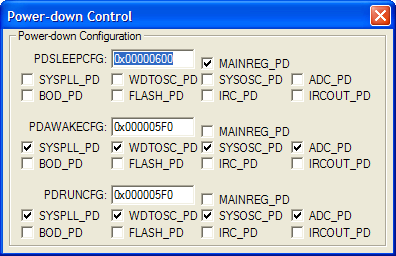

Power-down Control Dialog

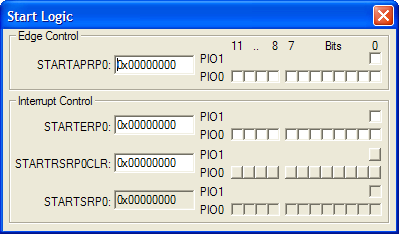

Start Logic Dialog

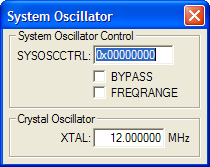

System Oscillator Dialog

The System Oscillator Control Dialog configures the frequency range for the system oscillator.

System Oscillator Control

- SYSOSCCTRL (System Oscillator Control Register) contains the following bit settings:

- BYPASS when set, the PLL input (SYS_OSC_CLK) is taken from the XTALIN and XTALOUT pins.

- FREQRANGE Determines frequency range for the low-power oscillator. If reset, 1-20 MHz. If set, 15-25MHz.

Crystal Oscillator

- XTAL contains the oscillator value in MHz.

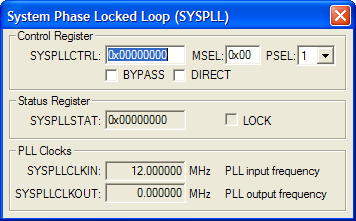

System Phase Locked Loop Dialog

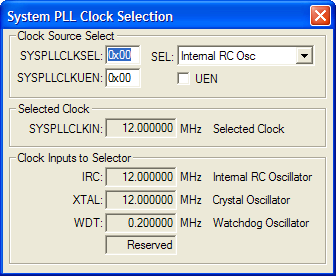

System PLL Clock Selection Dialog

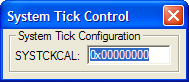

System Tick Control Dialog

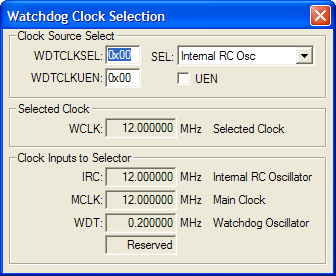

Watchdog Clock Selection Dialog

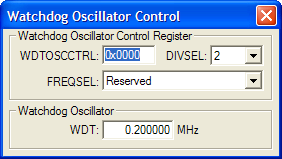

Watchdog Oscillator Control Dialog

The Watchdog Oscillator Control Dialog configures the frequency range for the watchdog oscillator.

Watchdog Oscillator Control

- WDTOSCCTRL (Watchdog Oscillator Control Register) contains the following bit settings:

- DIVSEL selects the divider value (2, 4 or 6) used to generate the watchdog oscillator claokc (WDT_OSC_CLK).

- FREQSEL Selects the watchdog oscillator frequency range.

Watchdog Oscillator

- WDT contains the oscillator value in MHz.

XTAL VTREG

Data Type: unsigned long

The XTAL VTREG contains the frequency of the oscillator (in Hertz) used to drive the microcontroller. The value is automatically set from the value specified in Project Options - Options for Target. However, you may change the value of XTAL using the command window. For example:

XTAL=33000000

You may also output the current value of XTAL using the following:

XTAL

XTAL may be used in calculations to synchronize external scripts with the simulated microcontroller.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |