|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Atmel AT91SAM7XC512 — Debug Unit

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

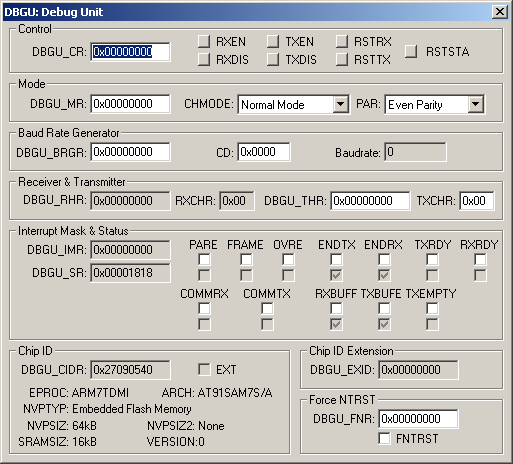

Debug Unit Dialog

The Debug Unit Dialog configures built-in Debug Unit.

Control

- DBGU_CR (Debug Control Register) displays the combined control information for the following:

- RXEN (Receiver Enable) enables the receiver.

- TXEN (Transmitter Enable) enables the transmitter.

- RXDIS (Receiver Disable) disables the receiver.

- TXDIS (Transmitter Disable) disables the transmitter.

- RSTRX (Reset Receiver) resets the receiver.

- RSTTX (Reset Transmitter) resets the transmitter.

- RSTSTA (Reset Status Bits) resets the Parity Error (PARE), Framing Error (FRAME), Overrun Error (OVRE) and Break Received (RXBRK) status bits.

Mode

- DBGU_MR (Mode Register) contains the following Mode settings:

- CHMODE (Channel Mode) selects normal, loopback, echo or remote loopback pin configurations.

- PAR (Parity Type) selects the generation of even, odd or no parity bits, mark or space, or multi-drop mode.

Baudrate Generator

- DBGU_BRGR (Baud Rate Generator Register) holds the following values:

- CD (Clock Divisor) contains the value divided into the clock that determines the baud rate.

- Baudrate displays the calculated baud rate.

Receiver & Transmitter

- DBGU_RHR (Receiver Holding Register) contains the RXCHR character.

- RXCHR (Received Character) holds the last character received.

- DBGU_THR (Transmitter Holding Register) contains the TXCHR character.

- TXCHR (Character to be Transmitted) holds the next character to be transmitted.

Interrupt Mask & Status

- DBGU_IMR (Interrupt Mask Register) holds the masking bits for all of the internal peripheral interrupts.

- DBGU_SR (Channel Status Register) hold the following composite status:

- PARE (Parity Error) set if the controller detects at least 1 false parity bit since the last Reset Status Bits command (RSTSTA).

- FRAME (Framing Error) set if the controller detects a framing error since the last Reset Status Bits command (RSTSTA).

- OVRE (Overrun Error) set if the controller detects an overrun condition since the last Reset Status Bits command (RSTSTA).

- ENDTX (End of Transmitter Transfer) is set if the End of Transmitter signal is active.

- ENDRX (End of Receiver Transfer) is set if the End of Receiver signal is active.

- TXRDY (Transmitter Ready) set if the transmit hold register (DBGU_THR) is empty and there is no break request pending.

- RXRDY (Receiver Ready) set when the USART receives at least 1 character and the receiver hold register (DBGU_RHR) is not empty.

- COMMTX (Debug Communication Channel Write Status) is set if the Debug Communication Channel Write signal is active.

- COMMRX (Debug Communication Channel Read Status) is set if the Debug Communication Channel Read signal is active.

- RXBUFF (Receive Buffer Full) is set if the Buffer Full signal from the PDC is active.

- TXBUFF (Transmit Buffer Full) is set if the Buffer Empty signal from the PDC is active.

- TXEMPTY (Transmitter Empty) set if there are no characters in the transmitter hold register.

Chip ID

- DBGU_CDIR (Chip ID Register) contains the chip identification information: processor type, NV memory size, Internal RAM size, NV memory type and chip architecture.

- EXT (Extension Flag) is set when an extended chip ID exists.

Chip ID Extension

- DBGU_EXID (Extension ID) displays the chip extension ID.

Force NTRST

- DBGU_FNR (Force NTRST Register) hold the following bit setting:

- FNTRST (Force NTRST) is set to hols the NTRST of the ARM processor's TAP controller low. If reset, the TAP controller is driven by the ICE_NRESET signal.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |