|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC2210/01 — SPI Interface

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

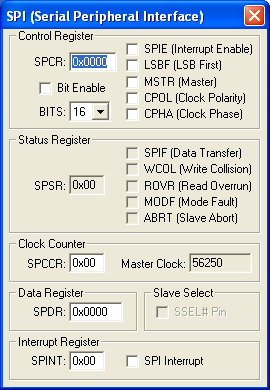

Serial Peripheral Interface Dialog

The Serial Peripheral Interface Dialog allows you to view and edit the Serial Peripheral Interface (SPI) simulator configuration. Simulation of this interface is controlled by the following groups:

Control Register Group

- SPCR (Serial Peripheral Control Register) contains the following bits that control the functions of the SPI:

- SPIE (SPI Interrupt Enable) is set to generate an interrupt when either the SPI Transfer Complete (SPIF) or Mode Fault (MODF) bits set.

- LSBF (LSB First) is set to transfer SPI data starting with bit 0. If reset, SPI starts data transfers with bit 7.

- MSTR (Master Mode) is set to configure the SPI as a Master. If reset, the SPI operates in Slave mode.

- CPOL (Clock Polarity) is set when the serial clock (SCK) is active low. If reset, SCK is active high.

- CPHA (Clock Phase) is set to sample data on the second clock edge. If CPHA is reset, data sampling starts on the first clock edge, and Slave Select (SSEL) signal determines the start and end of the data transfer cycle.

Status Register Group

- SPSR (SPI Status Register) monitors the SPI status. It contains the following read-only bits:

- SPIF (Data Transfer Complete) is set when the SPI completes a data transfer operation. This bit clears after this register and the data register (SPDR) are read.

- WCOL (Write Collision) is set when data is written to the SPI data register while a SPI data transfer is in progress.

- ROVR (Read Overrun) is set when the SPI receives data before it's read buffer is empty.

- MODF (Mode Fault) is set when the Slave Select (SSEL) goes active and the SPI is configured as a master.

- ABRT (Slave Abort) is set when the Slave Select (SSEL) signal goes inactive before a data transfer completes.

Clock Counter Group

- SPCCR (SPI Clock Counter Register) controls the SPI clock rate when the SPI is configured as a master. This value is the number of PCLK cycles that make up 1 SPI clock.

- Master Clock is the SPI clock value (SCK) based on the SPCCR setting.

Data Register Group

- SPDR (SPI Data Register) contains the either the data to be transmitted or the data received. In Master mode, writing to this register starts data transfer.

Slave Select Group

- SSEL# Pin (Slave Select) is the signal level at the slave select pin.

Interrupt Register Group

- SPINT (SPI Interrupt Register) contains the SPI interrupt flag setting.

- SPI Interrupt (SPI Interrupt Flag) is set by the SPI interface to generate an SPI interrupt.

SPI_IN VTREG

Data Type: unsigned char

The SPI_IN VTREG contains a byte which is received via the MCU SPI (Serial Peripheral Interface) port on the next SPI transfer. You may use this VTREG in a simulation script. For example:

signal void spi_func (void) {

while (1) {

wwatch (SPI_OUT);

printf ("SPI_OUT: %2.2X\n", (unsigned) SPI_OUT);

SPI_IN = SPI_OUT + 1;

}

}

This signal function returns the SPI byte send plus 1 on the next SPI transfer.

SPI_OUT VTREG

Data Type: unsigned char

The SPI_OUT VTREG contains a byte output via the MCU SPI (Serial Peripheral Interface) port. When your simulated program sends a byte via SPI, the SPI_OUT VTREG is set with the value output. You may monitor this VTREG in a simulation script. For example:

signal void spi_watcher (void) {

while (1) {

wwatch (SPI_OUT);

printf ("SPI_OUT: %2.2X\n", (unsigned) SPI_OUT);

}

}

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |