|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

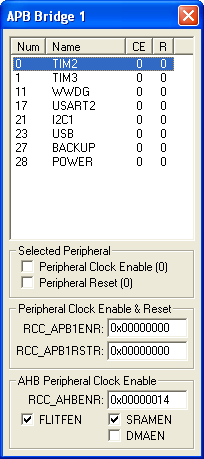

For STMicroelectronics STM32F103C6 — APB Bridge 1

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

APB Bridge 1 Dialog

The APB Bridge 1 dialog configures the low-power, APB Bridge of the STR7x device. This bridge interfaces the serial peripherals such as I2C, UART, USB, etc.

Selected Peripheral

- Peripheral Clock Disable is checked to disable the peripheral clock for the selected peripheral.

- Peripheral Reset is checked to reset the selected peripheral.

Clock Disable & Software Reset

- APB1_CKDIS (APB Clock Disable Register) contains the peripheral clock disable bit settings.

- APB1_SWRES (APB Software Reset Register) controls the reset of the APB 1 peripherals.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |