|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For STMicroelectronics STM32F103C8 — Power, Reset and Clock Control (PRCC)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

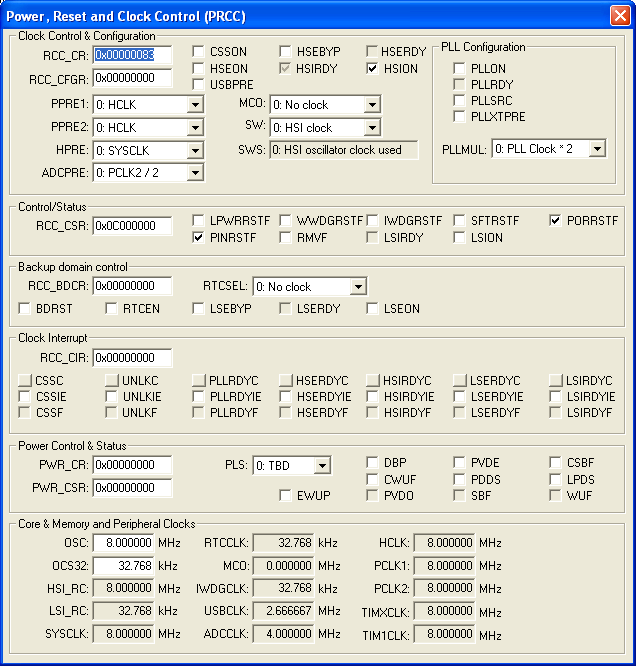

Power, Reset and Clock Control Unit Dialog

The Power, Reset and Clock Control Unit dialog configures the power saving mode, clock dividers, boot configuration and the core, memory and peripheral clocks of the ARM controller.

Clock Control & Flags

- PRCCU_CCR (Clock Control Register) contains the clock control bits.

- PRCCU_CFR (Clock Flag Register) contains the clock indicator flag bits.

- DIV2 (OSCIN Divided by 2) is set to divide CLK by 2.

- WFI_CKSEL (Wait For Interrupt Clock Select) is set to use CK_AF for MCLK during Low Power WFI, otherwise use CLK2/16 during Low Power WFI. Setting this bit effectively enables CKAF_SEL in WFI mode.

- CSU_CKSEL (CSU Clock Select) uses the clock from the PLL multiplier for the system clock when LOCK and VROK are set.

- CK2_16 (CLK2/16 Select) when set, uses CLK2 (or PLL output depending on CSU_CKSEL) as the source of RCLK. If reset, CLK2 divided by 16 is used.

- EN_STOP (Stop Interrupt Masking Bit) enables the stop interrupt request.

- EN_CK2_16 (CK2_16 Interrupt Masking Bit) enables the CK2_16 interrupt request.

- EN_CKAF (CKAF Interrupt Masking Bit) enables the CKAF interrupt request.

- EN_LOCK (Lock Interrupt Masking Bit) enables the LOCK interrupt request.

- SRESEN (Software Reset Enable) allows a software reset (HALT bit in PRCCU_SMR) if EN_HALT is also set.

- CKAF_SEL (Alternate Function Clock Select) is set to select the alternate function clock. When the selection is successful, the CKAF_ST status bit is set.

- STOP_I (Stop Interrupt Pending) is set when a Stop Interrupt request is pending.

- CK2_16_I (CK2_16 Switching Interrupt Pending) is set when a C2_16 Switching Interrupt request is pending.

- CKAF_I (CK_AF Switching Interrupt Pending) is set when a CKAF Switching Interrupt request is pending.

- LOCK_I (Lock Interrupt Pending) is set when a Lock Interrupt request is pending.

- LOPWFI (Low Power Mode During Wait For Interrupt) is set to force the device into Low Power Mode when an Wait For Interrupt (WFI) instruction executes.

- CKAF_ST (CK _AF Status) is set when CK_AF is the clock source. If reset, the PLL clock, CLK2 or CLK2/16 is the clock source depending on CSU_CKSEL.

- WKP_RES (External Wake Up Flag) is set when a reset occurs generated by a external wake-up event in standby mode.

- LVD_RES (Main Voltage Regulator LVD Reset Flag) is set when a main voltage regulator LVD reset occurs.

- RTC_ALARM (Real-Time Clock Alarm Reset Flag) is set when a real-time clock reset occurs.

- WDG_RES (Watchdog Reset Flag) is set when a watchdog reset occurs.

- SOFTRES (Software Reset Flag) is set when a software reset occurs.

- LOCK (PLL Locked) is set when the PLL is locked.

Power Control

- PRCCU_PWRCR (Power Control Register) contains the following control bits:

- WREN (Register Write Enable) allows the other register bits in PRCCU_PWRCR (this register) with write permission to be written.

- BUSY (Backup Logic Busy) is set to indicate that a previous write operation is still in progress. You cannot write to this register when this bit is set.

- WKUPALRM (Wakeup or Alarm Active) is set to indicate when the external WAKEUP pin or an internal wake-p source is active.

- VROK (Main Regulator OK) is set when the main voltage regulator is stable.

- FLASHLP (Flash Low Power Mode Select) if set, this bit disables burst mode and wait states are not generated for flashing. Default is reset, to allow burst mode and wait state generation.

- LVDDIS (Low Voltage Detector Disable) disables the low voltage detection so it cannot generate an MCU reset when a low voltage condition occurs. Software cannot clear this bit, only an MCU reset.

- OSCBYP (32KHz Oscillator Bypass Enable) when set, this bit turns off the 32KHz oscillator to reduce power consumption and allow external clocking.

- PWRDWN (Activate Power Down Mode) enables power down mode which turns off the main voltage regulator and power to the device kernel. The Low Power Regulator is still active.

- LPVRBYP (Low Power Regulator Bypass) when set, turns off the Low Power (Backup) Voltage Regulator. Power to the device kernel must be supplied via the V18 pin. NOTE: If set without an adequate power supply attached, the device could be damaged permanently.

- LPVRWFI (Low Power Regulator in Wait-For-Interrupt Mode.) when set, turns off the main voltage regulator in low power modes STOP and LP_WFI.

- VRBYP (Main Regulator Bypass) when set, turns off the main voltage regulator. Power to the device kernel must be supplied via the V18 pin. NOTE: If set without an adequate power supply attached, the device could be damaged permanently.

System Mode

- PRCCU_SMR (System Mode Register) contains the following control bits:

- WFI (Wait For Interrupt Mode) is set by the hardware to indicate an interrupt request is acknowledged by the External Interrupt Controller(EIC).

- HALT (Halt) when set, generates a software reset if SRESEN and ENHALT bits are set.

Peripheral Enable & Reset

- PRCCU_PER (Peripheral Enable Register) contains the following control bits:

- EMI (External Memory Interface Enable) is set to allow External Memory Interface(EMI) operation.

- USB (USB Peripheral Enable) is set to allow USB peripheral operation.

- PRCCU_PRSTR (Peripheral Reset Control Register) contains the following control bit:

- EMIRST(EMI Reset) is set to reset the External Memory Interface.

PLL Configuration

- PRCCU_PLL1CR (PLL 1 Configuration Register) contains the following control bits:

- FREEN(PLL Free Running Mode Enable) if set in conjuction with DX, provides a slow frequency back up clock selcted by the CSU_CKSEL. If reset, the PLL uses the MX and DX settings.

- FREF_RANGE(Reference Frequency Range Select) is set to configure the PLL for CLK2 frequencies greater than 3MHz. If reset, CLK2 frequencies between 1.5MHz and 3MHz may be used.

- MX(PLL Multiplier) selects the multiplier (12, 16, 20 or 24) for the PLL.

- DX(PLL Output Clock Divisor) selects the PLLCK divisor (1-7).

PLL Configuration (HDLC & USB)

- PRCCU_PLL2CR (PLL 2 Control Register) contains the following control bits:

- FRQRANGE(PLL 2 Frequency Range Select) is set to configure the PLL for CLK2 frequencies isbetween 3MHz-5MHz. If reset, CLK2 frequencies between 1.5MHz-3MHz may be used.

- MX(PLL 2 Multiplier) selects the multiplier (12, 16, 20 or 24) for the PLL.

- DX(PLL 2 Output Clock Divisor) selects the PLLCK divisor (1-7).

- PLLEN(PLL Select) is set to use the PLL clock. You may only set this bit when the PLL is locked (i.e. LOCK bit is set).

- USBEN(Enable PLL Clock to USB) is set to connect the USB reference clock to HCLK. If reset, the 48MHz reference clock is used for USBCLK.

- IRQMASK(Enable Interrupt Request to CPU on LOCK Transition) is set to generate an interruptrequest on any change in the LOCK bit status.

- IRQPEND(Interrupt Request to CPU on LOCK Transition Pending)

- LOCK(PLL2 Locked) is set by the hardware to indicate the PLL is locked.

Clock Divider Control

- PRCCU_MDIVR (MCLK Divider Control Register) contains the following control bits:

- FACT(Divisor Factor) selects the RCLK divisor (1, 2, 4 or 8) to generate MCLK.

- PRCCU_PDIVR (Peripheral Clock Divider Control Register) contains the prescaling factor for the APB clocks by setting the following control bits:

- FACT1(APB1 Peripheral Divisor) selects the RCLK divisor (1, 2, 4 or 8) to generate PCLK1.

- FACT2(APB2 Peripheral Divisor) selects the RCLK divisor (1, 2, 4 or 8) to generate PCLK2.

Boot Confguration

- PRCCU_BOOTCR (Boot Control Register) contains the following boot configuration bits:

- BOOT(Boot Mode) selects the boot mode (BOOT1 and BOOT0 pins).

- PKG64 (64-pin Package Die) if set, indicates the chip is mounted on a 64-pin package. If reset, a 144-pin package is used.

- HDLC (HDLC Active) is set when the HDLC controller is enabled.

- CAN (CAN Active) is set when the CAN controller is enabled.

- ADCEN (Enable ADC) is set to enable the ADC. A 1ms startup delay is required after enabling the ADC.

- SPI0EN (Enable SPI0) is set to enable the SPI 0 controller. Pins P0.1 to P0.3 are assigned to SPI 0. UART3 and I2C1 are not available while using this controller.

- LPOWDBGEN (Enable Reserved Debug Features for STOP Mode) is set to force an exit from STOP mode and enabling internal clocks, allowing an emulator to take control of the MCU.

- USBFILTEN (Enable USB Standby Filter) is set to enable the low-pass filter to improve immunity to noise while the USB is in STANDBY mode.

Core & Memory and Peripheral Clocks

- CK (External Oscillator) is the value (in MHz) of the external oscillator used for the source clock signal.

- RTCX(Real-Time Clock) is the value (in kHz) of the external oscillator used for input to the real-time clock.

- RCLK is the output of either the system PLL, or the CK_AF alternate clock source is enabled.

- MCLK (Main Clock) is the clock used for the CPU, internal memory, EMI and the PRCCU.

- PCLK1 is derived from RCLK and used for APB1 peripherals.

- PCLK2 is derived from RCLK and used for APB2 peripherals.

HDLC & USB Clocks

- HCLK contains the clock value present at the HCLK pin.

- USBCLK contains the clock value present at the USBCLK pin.

- HDLC Clock displays the clock value connected to the HDLC peripheral.

- USB clock (Main Clock) displays the clock value connected to the USB peripheral.

16MHz Clock Input VTREG

Data Type: unsigned long

A/D Converter Clock VTREG

Data Type: unsigned long

HDLC Clock Input VTREG

Data Type: unsigned long

Internal Watchdog Clock VTREG

Data Type: unsigned long

Real-Time Clock Output VTREG

Data Type: unsigned long

System Clock VTREG

Data Type: unsigned long

USB Clock VTREG

Data Type: unsigned long

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |