|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Silicon Laboratories, Inc. C8051T601 — CPU Reset

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

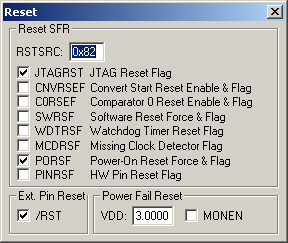

Reset Dialog

The Reset dialog displays and configures simulation of the system reset source register, power fail and external reset functions.

Reset SFR

- RSTSRC (Reset Source Register) contains the following settings:

- JTAGRST (JTAG Reset) is set when the source of the last reset is the JTAG device.

- CNVRSEF (Convert Start Reset Source Enable and Flag) is set tp allow CNVSTR to be a reset source. When read, this bit signifies the source of the last reset was a write due to a CNVSTR reset.

- C0RSEF (Comparator 0 Reset Enable and Flag) is set to allow Comparator 0 to be a reset source. When read, this bit signifies the source of the last reset was a write due to a Comparator 0 reset.

- SWRSF (Software Reset Force and Flag) is set to force and internal reset. When read, this bit signifies the source of the last reset was a write to this bit.

- WDTRSF (Watchdog Timer Reset Flag) is set when the source of the last reset was the Watchdog Timer (WDT).

- MCDRSF (Missing Clock Detector Flag) is set when the source of last reset was a timeout from the Missing Clock Detector.

- PORSF (Power-On Reset Force and Flag) is set to force a Power On Reset (POR). When read, this bit set signifies the source of the last reset was a POR.

- PINRSF (HW Pin Reset Flag) is set when the source of last reset was /RST pin.

Ext. Pin Reset

- /RST (Reset Pin)

- is set to simulate a hardware reset to the microcontroller.

Power Fail Reset

- VDD is the digital supply voltage.

- MONEN (VDD Monitor Enable Pin) is pulled high to enable the VDD monitor. This monitor forces a system reset when the VDD is less than 2.7 volts.

RST VTREG

Data Type: bit

RST simulates the reset pin of the MCU. This pin is bi-directional, allowing an external reset input or a Power On Reset (POR), generated internally, to be output on this pin.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |