|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC2364 — Vectored Interrupt Controller (VIC)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

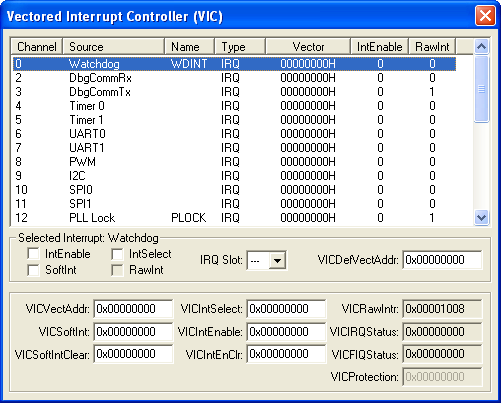

Vectored Interrupt Controller Dialog

The Vectored Interrupt Controller Dialog displays the status of all simulated MCU interrupts. The source, channel, type, vector and interrupt state for each interrupt is displayed. You may select and configure each interrupt using the following control groups:

Selected Interrupt

The checkboxes in this group control or reflect the highlighted interrupt.

- IntSelect is set if the highlighted interrupt is an FIQ interrupt. If reset, it is a vectored IRQ interrupt.

- SoftInt is set to trigger a software interrupt for the highlighted interrupt.

- IntEnable Enables the highlighted interrupt.

- RawInt is set if any interrupt request occurs for the highlighted interrupt, whther enabled or not.

Vectored IRQ

- Slot (Slot Number) selects a Slot Number to be assigned to a Channel when the Enable box is checked.

- Channel (Channel Number) selects the Channel number that receives the Slot Number assignment.

- Enable when set, assigns the current Slot Number to the selected Channel. Resetting this checkbox unassigns a Slot.

- VICVectCntlx (Vector 0-15 Control Register) contains the interrupt request slot number assigned to vectored IRQ x and the the IRQ enable bit.

- VICVectAddrx (Vector Address 0-15 Register) contains the address of the interrupt service routine for the vectored interrupts 0-15.

- VICVectAddr (Vector Address Register) contains the address of the interrupt service routine for the highest priority vectored IRQ.

- VICDefVectAddr (Default Vector Address Register) is the interrupt service routine for non-vectored IRQ interrupts.

- VICProtection (Protection Enable Register) if set, software must be in Privileged mode to access the Vectored Interrupt Controller (VIC).

- VICSoftInt (Software Interrupt Register) forces an interrupt if the corresponding bit is set.

- VICSoftIntClear (Interrupt Clear Register) releases the forced software interrupt if the corresponding bit is set.

- VICIntSelect (Interrupt Select Register) contains the type of interrupt. Bits that are set represent non-vectored FIQ interrupts. Bits that are reset represent vectored IRQ interrupts.

- VICIntEnable (Interrupt Enable Register) enables IRQ or FIQ interrupts if the corresponding bit is set.

- VICIntEnClr (Interrupt Enable Clear Register.) resets an enabled IRQ or FIQ interrupts if the corresponding bit is set

- VICRawIntr (Raw Interrupt Status Register) displays the state of all interrupts, enabled or not.

- VICIRQStatus (IRQ Status Register) displays the state of enabled IRQ (vectored) interrupts.

- VICFIQStatus (FIQ Status Requests) displays the state of enabled FIQ (non-vectored) interrupts.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |