|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Infineon XC164S-16F — High-Speed Synchronous Serial Interface SSC0

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

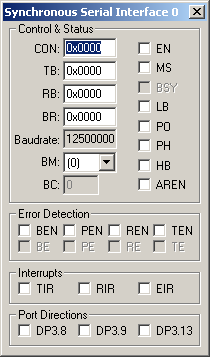

Synchronous Serial Interface 0 Dialog

The Synchronous Serial Interface 0 dialog allows you to edit the configuration of the Synchronous Serial Interface. The controls in this dialog are separated into several logical groups.

Control & Status

- CON (SSC Control Register) contains the following control and status settings:

- EN (Enable) is set to enable the Synchronous Serial Interface.

- MS (Master Select) is set to generate shift clocking from SCLK.

- BSY (Busy Flag) indicates data transfer is in progress.

- LB (Loop Back Control) is set to connect received input to transmitted output.

- PO (Clock Polarity Control) is set make the clock line low-active and the leading clock edge is a high-to-low transition.

- PH (Clock Phase Control) is set to latch receive data on the leading clock edge and shift on the trailing edge. If reset, Shift receive data on the leading clock edge and latch on the trailing edge.

- HB (Heading Control) is set to transmit or receive MSB first. if reset, LSB is first.

- AREN (Automatic Reset Enable) is set to automatically reset the SSC on a baudrate error.

- TB (Transmit Buffer) contains the transmit data.

- RB (Receive Buffer) contains the received data.

- BR (Baudrate Timer / Reload Register) contains the 13-bit baudrate timer.

- Baudrate is the generated baud rate.

- BM (Data Width Selection) selects the transfer data widths from 2-bits to 16-bits.

- BC (Bit Count Field) displays the bit-shift count.

Error Detection

- BEN (Baudrate Error Enable) is set to check for baudrate errors.

- PEN (Phase Error Enable) is set to check for phase errors.

- REN (Receive Error Enable) is set to check for receive errors.

- TEN (Transmit Error Enable) is set to check for transmission errors.

- BE (Baudrate Error Flag) is set when the baudrate from the slave varies more than a factor of .5 or 2.

- PE (Phase Error Flag) is set when the received data changes sampling clock edge.

- RE (Receive Error Flag) is set when data is received before the receive buffer is read.

- TE (Transmit Error Flag) is set when a transfer starts before the slaves transmit buffer is updated.

Interrupts

- TIR (Transmit Interrupt) is set before the last bit of an asynchronous frame is transmitted, or after the last bit of a synchronous frame has been transmitted.

- RIR (Receive Interrupt) is set when the received frame is moved to RBUF.

- EIR (Error Interrupt) is set when a receive or transmit error occurs.

Port Directions

- DP3.8 in Master mode, is set for input, in Slave mode, is reset for output.

- DP3.9 in Master mode, is set for output, in Slave mode, is reset for input.

- DP3.13 in Master mode, is set for output, in Slave mode, is reset for input.

SSCCLK VTREG

Data Type: unsigned int

SSCIN VTREG

Data Type: unsigned int

SSCOUT VTREG

Data Type: unsigned int

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |