|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Infineon XC164GM-8F — Capture/Compare Unit CAPCOM6 with T12, T13

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

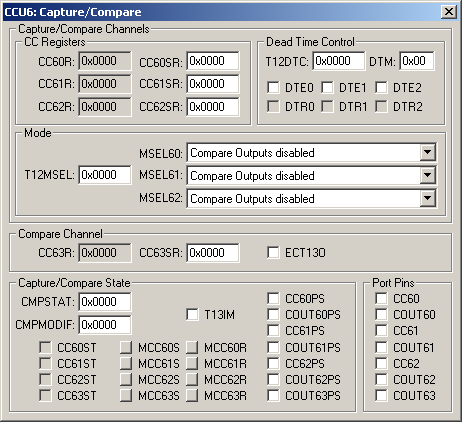

CCU6: Capture/Compare Dialog

The CCU6: Capture/Compare dialog allows you to view and interactively configure the sixteen channels of the Capture/Compare Unit 6. Typically, your embedded program writes values to SFRs to configure the CAPCOM Unit and the CAPCOM channels. You may use this dialog to view and confirm the CAPCOM settings.

CC Registers

- CC6xR (Channel x Capture/Compare Register) contains the value of the CAPCOM register for channel x. The values in these registers are copied from the shadow register values.

- CC6xSR (Channel x Capture/Compare Shadow Register) specifies the value to be loaded into the CC6xR register.

Dead Time Control

- T12DTC (Timer 12 Dead Time Control Register) contains the DTE and DTR bit settings for channels 0-2, and the DTM value.

- DTM (Dead Time Control Register) sets the delay to be used between switching from a passive state to an active state.

- DTEx (Dead Time Generation Enable x) is set to enable dead-time generation for channel x.

- DTRx (Dead Time Run Flag x) is set when the dead-time counter for channel x is running.

Mode

- T12MSEL (T12 Mode Select Register) contains the MSEL60, MSEL61 and MSEL62 mode selection setting.

- MSEL6x (Capture/Compare Mode Selection Channels 0-2) selects the operating mode for each CCU channel.

Compare Channel

- CC63R (Channel 3 Compare Register) contains the value compared to the T13 counter.

- CC63SR (Channel 3 Compare Shadow Register) contains the values to be transferred to the CC63R compare register.

- ECT13O (Enable Compare Timer T13 Output) is set to allow the signal at COUT63 to reflect T13 output.

Capture/Compare State

- CMPSTAT (Compare State Register) contains the T13IM, CC6xPS, CC6xST and COUT6xPS settings.

- CMPMODIF (Compare State Modification Register) contains the MCC6xS and MCC6xR settings.

- T13IM (T13 Inverted Modulation Control) inverts signal CC63_O for modulating CC6x and COUT6x signals.

- CC6xST (T13/T12 Compare State Bit) if set during compare mode, the timer count is greater than the compare value. If set in capture mode, it indicates a detection of the selected edge.

- MCC6xS (Capture/Compare Channel x Status Set Bit) clicking this button sets the CC6xST bit.

- MCC6xR (Capture/Compare Channel x Status Reset Bit) clicking this button clears the CC6xST bit.

- CC6xPS and COUT6xPS (Passive State Select for Compare Output) is set to make CC6x and COUT6x outputs passive level driven.

Port Pins

- CC6x and COUT6x (Capture/Compare Channel x Output) are the CCU channel output pins.

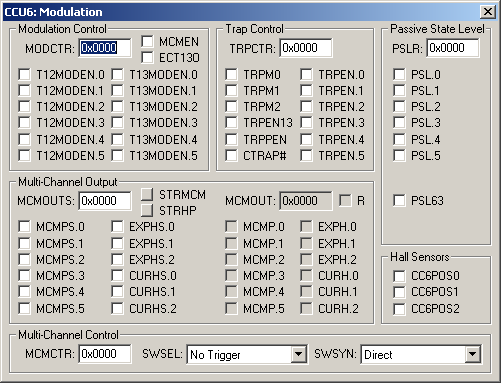

CCU6: Modulation Dialog

The CCU6: Modulation dialog allows you to view and interactively configure the modulation, trap and passive state level controls of Capture/Compare Unit 6.

Modulation

- MODCTR (Modulation Control Register) contains the following modulation control bits:

- MCMEN (Multi-Channel Mode Enable) is set to enable modulation control.

- ETC13O (Enable Compare Timer T13 Output) is set to allow the signal at COUT63 to reflect T13 output.

- T12MODEN.x (T12 Modulation Enable Bits 0-5) is set to modulate the corresponding output to Timer 12.

- T13MODEN.x (T13 Modulation Enable Bits 0-5) is set to modulate the corresponding output to Timer 13.

Trap Control

- TRPCTR (Trap Control Register) contains the trap configuration bits described below:

- TRPMx (Trap Mode Control Bits 0-1) selects whether the trap is terminated using a Timer 12 or Timer 13 match.

- TRPM2 (Trap Mode Control Bit 2) is set to allow software initiate the trap. If reset, it is initiated by hardware.

- TRPEN13 (Trap Enable Control for T13 Output) is set to enable the trap function for Timer 13 output signal CC63.

- TRPPEN (Trap Pin Enable Control)

- CTRAP# is the input signal controlling the trap function.

- TRPEN.x (Trap Enable Control for T12 Outputs) is set to enable the trap function for Timer 12 output signals COUT62, CC62, COUT61, CC61, COUT60 and CC60.

Passive State Level

- PSLR (Passive State Level Register) contains the following passive state control bits:

- PSL.x (T12 Outputs Passive State Level Control) is set to define the passive level for output pins COUT62, CC62, COUT61, CC61, COUT60 and CC60 to 1.

- PSL63 (T13 Output COUT63 Passive State Level Control) is set to define the passive level for output pin COUT63 to 1.

Multi-Channel Output

- MCMOUTS (Multi-Channel Mode Output Shadow Register) contains the following bits:

- STRMCM (Shadow Transfer Request for MCMPS) is set to move MCMPS data to the MCMP.

- STRHP (Shadow Transfer Request for the Hall Patterns) is set to move data from CURHS and EXPHS to CURH and EXPH.

- MCMPS.x (Multi-Channel PWM Pattern Shadow Field) contains the multi-channel PWM pattern to be loaded into MCMP.

- EXPHS.x (Expected Hall Pattern Shadow Field) contains the expected pattern to be loaded into EXPH.

- CURHS.x (Current Hall Pattern Shadow Field) contains the current pattern to be loaded into CURH.

- MCMOUT (Multi-Channel Mode Output Register) contains the following bits:

- R (Reminder Flag) is set when trigger source requests a shadow transfer from bit field MCMPS to MCMP.

- MCMP.x (Multi-Channel Modulation Pattern Bits 0-5) are set to define the modulation pattern for output pins COUT62, CC62, COUT61, CC61, COUT60 and CC60.

- EXPH.x (Expected Hall Pattern Bits 0-2) contains the expected hall pattern to be compared to the sampled hall pattern.

- CURH.x (Current Hall Pattern Bits 0-2) contains the current hall pattern

Hall Sensors

- CC6POSx are the 3 Hall pattern sensor inputs.

Multi-Channel Control

- MCMCTR (Multi-Channel Mode Control Register) contains the following multi-channel control bits:

- SWSEL (Switching Selection) selects the trigger source for the shadow transfer.

- SWSYN (Switching Synchronization) triggers a requested shadow transfer from MCMPS to MCMP.

Timer 12 Dialog

The Timer 12 Dialog allows you to view and change the SFRs associated with Timer 12. This timer is used to generate the time base for the Capture/Compare Unit of the MCU.

Control

- TCTR0 (Timer Control Register 0) contains basic timer control settings common to Timer 12 and Timer 13.

- TCTR2 (Timer Control Register 2) controls synchronization and single-shot functions of Timer 12 and Timer 13.

- TCTR4 (Timer Control Register 4) contains the run control and reset bits for Timer 12 and Timer 13.

- T12CLK (Timer 12 Input Clock Select) selects the input clock frequency for Timer 12.

- T12R (Timer 12 Run Bit) when set, Timer 12 is running.

- STE12 (Timer 12 Shadow Transfer Enable) when set, initiates a Timer 12 shadow transfer event.

- CDIR (Count Direction of Timer 12) when set, Timer 12 counts down. When reset, Timer 12 counts up.

- CTM (Timer 12 Operating Mode) when set, Timer 12 operates in center-aligned mode. In this mode, T12 counts down after detecting a perio-match and counts up after detecting a one-match. When reset, Timer 12 operates in edge-aligned mode. In this mode, T12 only counts up to the period-match value, then restarts counting at zero.

- T12SSC (Timer 12 Single-Shot Control) when set, Timer 12 operates in single-shot (stop counting after one timer period) mode.

- T12PRE (Timer 12 Prescaler Bit) when set, enables a prescaler factor of 256 for Timer 12.

- T12HR (CCU Timer 12 Hardware Run Signal) when set, starts Timer 12 running. IST12HR controls which pin (T12HR _0, T12HR _1 or T12HR _2) generates this signal.

- T12RR (Timer 12 Run Reset) when set, T12R clears and Timer 12 stops counting.

- T12RS (Timer 12 Run Set) when set, T12R is set.

- T12RES (Timer 12 Reset) when set, zeroes the timer/counter(T12).

- DTRES (Dead-Time Counter Reset) when set, zeroes the 3 dead-time counters.

- T12STR (Timer 12 Shadow Transfer Request) when set, sets STE12, enabling shadow transfers.

- T12STD (Timer 12 Shadow Transfer Disable) when set, clears STE12, disabling shadow transfers.

Timer & Period

- T12 (Timer/Counter) contains the current count value of Timer 12.

- T12PR (Timer 12 Period Register) contains the value matched to the T12 counter to trigger a Timer 12 period-match event.

Int. Node 2

- ECCIP2 (CCU6 Interrupt Node Pointer 2 Enable) when set, enables interrupt node pointer 2.

Interrupts

- T12OM (Timer 12 One-Match) is set to indicate a Timer 12 one-match event occurred.

- T12PM (Timer 12 Period-Match) is set to indicate a Timer 12 period-match event occurred.

- ST12OM (Set Timer 12 One-Match) when set, forces the one-match event flag(T12OM).

- ST12PM (Set Timer 12 Period-Match) when set, sets the period-match event flag(T12PM).

- RT12OM (Reset Timer 12 One-Match) when set, clears the one-match event flag(T12OM).

- RT12PM (Reset Timer 12 Period-Match) when set, clears the period-match event flag(T12PM).

- ENT12OM (Enable Timer 12 One-Match) when set, allows an interrupt to be generated when a one-match event occurs on Timer 12.

- ENT12PM (Enable Timer 12 Period-Match) when set, allows an interrupt to be generated when a period-match event occurs on Timer 12.

Timer 13 Dialog

The Timer 13 Dialog allows you to view and change the SFRs associated with Timer 13. This timer is used to generate the time base for the Capture/Compare Unit of the MCU.

Control

- TCTR0 (Timer Control Register 0) contains basic timer control settings common to Timer 12 and Timer 13.

- TCTR2 (Timer Control Register 2) controls synchronization and single-shot functions of Timer 12 and Timer 13.

- TCTR4 (Timer Control Register 4) contains the run control and reset bits for Timer 12 and Timer 13.

- T13CLK (Timer 13 Input Clock Select) selects the input clock frequency for Timer 13.

- T13R (Timer 13 Run Bit) when set, Timer 13 is running.

- STE13 (Timer 13 Shadow Transfer Enable) when set, initiates a Timer 13 shadow transfer event.

- T13SSC (Timer 13 Single-Shot Control) when set, Timer 13 operates in single-shot (stop counting after one timer period) mode.

- T13PRE (Timer 13 Prescaler Bit) when set, enables a prescaler factor of 256 for Timer 13.

- T13HR (CCU Timer 13 Hardware Run Signal) when set, starts Timer 13 running. IST13HR controls which pin (T13HR _0, T13HR _1 or T13HR _2) generates this signal.

- T13TEC (Timer 13 Trigger Event Control) selects which Timer 12 trigger event starts the T13 counter.

- T13TED (Timer 13 Trigger Event Direction) selects the direction (up or down) T12 (Timer 12) must be counting to start a T13 event.

- T13RR (Timer 13 Run Reset) when set, T13R clears and Timer 13 stops counting.

- T13RS (Timer 13 Run Set) when set, T13R is set.

- T13RES (Timer 13 Reset) when set, zeroes the timer/counter(T13).

- T13STR (Timer 13 Shadow Transfer Request) when set, sets STE13, enabling shadow transfers.

- T13STD (Timer 13 Shadow Transfer Disable) when set, clears STE13, disabling shadow transfers.

Timer & Period

- T13 (Timer/Counter) contains the current count value of Timer 13.

- T13PR (Timer 13 Period Register) contains the value matched to the T13 counter to trigger a Timer 13 period-match event.

Int. Node 3

- ECCIP3 (CCU6 Interrupt Node Pointer 3 Enable) when set, enables interrupt node pointer 3.

Interrupts

- T13OM (Timer 13 One-Match) is set to indicate a Timer 13 one-match event occurred.

- T13PM (Timer 13 Period-Match) is set to indicate a Timer 13 period-match event occurred.

- ST13OM (Set Timer 13 One-Match) when set, forces the one-match event flag(T13OM).

- ST13PM (Set Timer 13 Period-Match) when set, sets the period-match event flag(T13PM).

- RT13OM (Reset Timer 13 One-Match) when set, clears the one-match event flag(T13OM).

- RT13PM (Reset Timer 13 Period-Match) when set, clears the period-match event flag(T13PM).

- ENT13OM (Enable Timer 13 One-Match) when set, allows an interrupt to be generated when a one-match event occurs on Timer 13.

- ENT13PM (Enable Timer 13 Period-Match) when set, allows an interrupt to be generated when a period-match event occurs on Timer 13.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |