|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Infineon XC886CM-8FF — A/D Converter (8 channel 8/10-bit)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

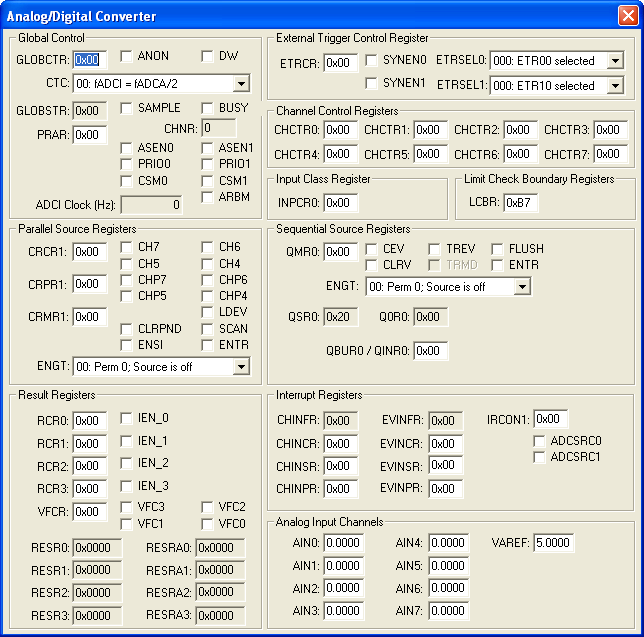

Analog/Digital Converter Dialog

The Analog/Digital Converter dialog displays and allows you to edit the configuration of the A/D converter.

Global Control

- GLOBECTR (Global Control Register)

- CTC (Conversion Time Control) displays and allows you to select the A/D Converter clock divisor to 2, 3, 4 or 32.

- ANON (Analog Part Switched On)

- DW (Data Width)

- GLOBESTR (Global Status Register) contains the BUSY, SAMPLE and CHNR settings.

- PRAR (Priority and Arbitration Register) contains the following bit settings:

- ASENx (Arbitration Slot x Enable) enables the corresponding arbitration slot, 0 or 1.

- PRIO0 (Priority of Request Source 0) is set to define sequential request source 0 as high priority.

- PRIO1 (Priority of Request Source 1)is set to define parallel request source 1 as high priority.

- CSM0 (Conversion Start Mode of Request Source 0) is set to select cancel-inject-repeat mode for sequential request source 0. If reset, wait-for-start mode is selected.

- ARBM (Arbitration Mode) is set to start arbitration when there is a pending conversion request. If reset, permanent arbitration mode is selected.

- CSM1 (Conversion Start Mode of Request Source 1) is set to select cancel-inject-repeat mode for parallel request source 1. If reset, wait-for-start mode is selected.

- ADC1 Clock displays the A/D clock frequency in Hz.

External Trigger Control Register

- ETRCR (External Trigger Control Register) contains the following control bits:

- SYNENx (Synchronization Enable) when set, enables external trigger input synchronization.

- ETRSELx (External Trigger Selection for Request Source x) defines the external

Channel Control Registers

- CHCTRx (Channel Control Register 0-7) controls which result register (0-3) and limit check option is used for each channel.

Input Class Register

- INPCR0 (Input Class Register) contains the Sample Time Control (STC) which extends the input channel sample time by this value.

Limit Check Boundary Register

- LCBR (Limit Check Boundary Register) contains 2, 4-bit values representing the 4 most-significant bits of the 8-bit or 10-bit boundary limit which is compared to the ADC conversion result.

Parallel Source Register

- CRCR1 (Conversion Request Control Register 1) contains the channel bits (CH4-CH7).

- CHx (Channel Bits 4-7) when set, requests a conversion for analog channel 4, 5, 6 or 7.

- CRPR1 (Conversion Request Pending Register 1)

- CHPx (Channel Pending Bit 4-7) when set, indicates a conversion is requested for an analog channel.

- CRMR1 (Conversion Request Mode Register 1) contains the following control bits:

- CLRPND (Clear Pending Bits) setting this bit resets all the pending request bits in CRPR1.

- ENSI (Enable Source Interrupt) when set, enables the request source interrupt.

- LDEV (Generate Load Event) when set, loads the pending register(CRPR1) with the contents of the control register(CRCR1).

- SCAN (Autoscan Enable) when set, enables the automatic event reload for channels 4-7, without requiring an external trigger.

- ENTR (Enable External Trigger) when set, triggers a load event on a rising edge of REQTR.

- ENGT (Enable Gate) when set, enables conversion requests.

Sequential Source Register

- QMR0 (Queue Mode Register) contains the following control bits:

- CEV (Clear Event Bit) when set, clears the event(EV) bit.

- CLRV (Clear V Bits) when set, clears the valid data bit(V) in Q0R0, if the QBUR0 valid(V) bit is already 0, otherwise it clears the QBUR0 valid(V) bit.

- TREV (Trigger Event) when set, starts a conversion request.

- TRMD (Trigger Mode) determines when the signals REQPND and REQCHNRV become active.

- FLUSH (Flush Queue) when set, clears all valid(V) bits in the queue and the event(EV) bit.

- ENTR (Enable External Trigger) when set, triggers a load event(EV) on a rising edge from the external trigger input(REQTR).

- ENGT (Enable Gate) when set, enables conversion requests.

- QSR0 (Queue Status Register) displays the byte containing the event detected(EV, QSR0.4) and the queue empty(EMPTY, QSR0.5) status bits.

- Q0R0 (Queue 0 Register 0) contains the EXTR, ENSI, RF, V and REQCHNR bit settings.

- QBUR0/QINR0 (Queue Backup Register 0/Queue Input Register 0) QBUR0/QINR0 displays status of a sequential request. Writing to QBUR0/QINR0 starts a sequential request.

Result Registers

- RCRx (Result Control Register x) contains IEN and other result register control bits.

- IEN_x (Interrupt Enable) when set, enables the event interrupt for this result register.

- VFCR (Valid Flag Clear Register) contains the VFCx settings.

- VFCx (Clear Valid Flag for Result Register x) when set, clears the corresponding bit in the result registers (RESRx and RESRAx).

- RESRx (Normal Read View) contains the 8-bit or 10-bit result of the conversion.

- RESRAx (Accumulated Read View) contains the accumulated 9-bit or 11-bit result of the conversion.

Interrupt Registers

- CHINFR (Channel Interrupt Flag Register) contains the flags that set when an channel 0-7 interrupt occurs.

- CHINCR (Channel Interrupt Clear Register) when set, clears the corresponding channel interrupt flag in CHINFR.

- CHINSR (Channel Interrupt Set Register) when set, generates an interrupt and sets the corresponding channel interrupt flag in CHINFR.

- CHINPR (Channel Interrupt Node Pointer Register) defines which SR line (SR0 or SR1) activates during a channel 0-7 interrupt.

- EVINFR (Event Interrupt Flag Register) contains the flags that set when an event interrupt occurs.

- EVINCR (Event Interrupt Clear Flag Register) when set, clears the corresponding event interrupt flag in EVINFR.

- EVINSR (Event Interrupt Set Flag Register) when set, sets the corresponding event interrupt flag in EVINFR.

- EVINFR (Event Interrupt Node Pointer Register) defines which SR line (SR0 or SR1) activates during an event 0 interrupt.

- IRCON1 (Interrupt Request Register 1) indicates active requests for both ADC interrupts(ADCSRC0 and ADCSRC1).

- ADCSRC0 (Interrupt Request 0 Flag for ADC) when set and interrupt request has occurred for source 0.

- ADCSRC1 (Interrupt Request 1 Flag for ADC) when set and interrupt request has occurred for source 1.

The Analog Input Channels group contains an input box for each analog channel is displayed at the bottom of the dialog. These boxes display the current voltage for the channel. You may edit the value to specify a new input voltage for that channel. When the A/D Converter subsequently performs a conversion using that channel, the input voltage specified is converted into a digital value. VAREF is the supply voltage reference.

AINx VTREG

Data Type: float

The AINx VTREGs set the analog input voltages for simulated A/D converters. The AINx VTREGs represent the inputs to the analog input pins of the MCU for analog input 0, 1, 2, and so on. AIN0 sets the input voltage for analog input #0, AIN1 sets the input voltage for analog input #1, etc. If you have properly configured the analog inputs, the following commands (typed in the debugger's Command Window) input the voltages specified.

AIN0 = 0.000 /* Analog Input 0 = 0.000 volts */ AIN1 = 2.500 /* Analog Input 1 = 2.500 volts */ AIN2 = 4.999 /* Analog Input 2 = 4.999 volts */

You may also enter the analog input voltages using the A/D Converter Dialog which is accessable from the Peripherals menu. You may create a debugger signal function to periodically change the value of the A/D input. The following signal function increases the A/D Channel 1 input voltage by 0.1 volts each second.

signal void AIN1_sig (void) {

float f;

for (f = 0.0; f < 5.0; f += 0.1)

{

swatch (1.0); // Delay 1 second

AIN1 = f; // Set AIN1 Voltage

}

}

VAREF VTREG

Data Type: float

The VAREF VTREG contains the A/D Reference Voltage (the maximum voltage allowed for A/D conversions).

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |