|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Infineon XC886C-8FF — Interrupts 15S/4L (including External, Extended and NMI)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

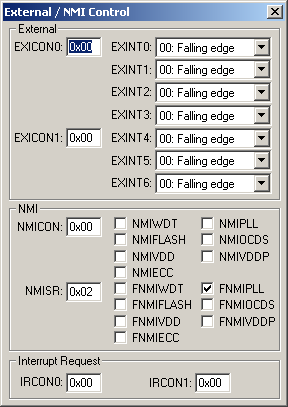

External / NMI Control Dialog

The External / NMI Control Dialog shows the current state of the on-chip external interrupt and non-maskable interrupt controllers. You may change the configuration of these controllers using the controls in this dialog.

External

- EXICON0 (External Interrupt Control Register 0) holds the parameters that control the external interrupts 0-3 (EXINT0-EXITN3).

- EXICON1 (External Interrupt Control Register 1) holds the parameters that control the external interrupts 4-6 (EXINT4-EXITN6).

- EXINTx (External Interrupts 0-6 Trigger Select) selects the interrupt to occur with a falling edge, rising edge or falling edge and rising edge.

NMI

- NMICON (NMI Control Register) holds the following settings:

- NMIWDT Enables the Watchdog Timer NMI.

- NMIFLASH Enables the Flash Timer NMI.

- NMIVDD VDD Prewarning NMI.

- NMIECC Enables the Error Correction Code NMI.

- NMIPLL Enables the Phase-Locked Loop Loss of Lock NMI.

- NMIOCDS Enables the On-Chip Debug Support NMI.

- NMIVDDP Enables the VDDP Prewarning NMI.

- NMISR (NMI Status Register) holds the following status bits:

- FNMIWDT (Watchdog Timer NMI Flag) is set when a watchdog timer prewarning occurs.

- FNMIFLASH (Flash Timer NMI Flag) is set when the flash time overflows.

- FNMIVDD (VDD Prewarning NMI Flag) is set when the VDD is below 2.3 volts.

- FNMIECC (ECC NMI Flag) is set when an Error Correction Code error occurs.

- FNMIPLL (PLL NMI Flag) when set, indicates that the Phase-Locked Loop has lost the lock on the external oscillator.

- FNMIOCDS (OCDS NMI Flag) is set when a JTAG-receiving or user interrupt is requested in monitor mode.

- FNMIVDDP (VDDP Prewarning NMI Flag) is set when the VDD is below 4.0 volts on 5.0 volt power.

Interrupt Request

- IRCON0 (Interrupt Request Register 0) Bits 0-6 are set in this register to indicate an interrupt request is active for External Interrupt 0-6, respectively.

- IRCON1 (Interrupt Request Register 1) indicates active requests for SSC Error(EIR), SSC Transmit(TIR), SSC Receive(RIR) and both ADC interrupts.

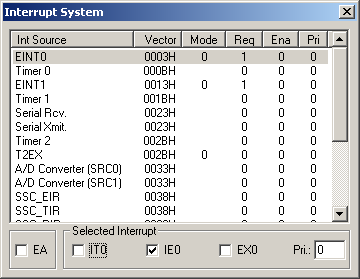

Interrupt System Dialog

The Interrupt System dialog (available from the Peripherals menu) displays the status of all simulated MCU interrupts. The interrupt source, vector address, mode, request, priority, and enabled status are displayed. Clicking on a column header orders the interrupt list based on the selected column. You may use this dialog to manually change the interrupt configuration. Select the desired interrupt source from the list.

The Selected Interrupt group displays the control bits assigned to that interrupt. Click on the desired check box to immediately effect the change. You may even trigger an interrupt by clicking on its request bit.

NMI VTREG

Data Type: unsigned char

THE NMI VTREG contains the state of the NMI pin on the simulated MCU. Normally, the NMI pin is high (indicating that there is no non-maskable interrupt condition). NMI goes low to signal a non-maskable interrupt. Enter the following in the Command window to trigger an NMI Trap using the NMI VTREG.

NMI=0

Enter the following to return the NMI pin to a high level.

NMI=1

Note that on some devices the NMI pin must be low to enter Power Down Mode.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |