|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Infineon XC888-8FF — Capture/Compare Unit 6 (CCU6)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

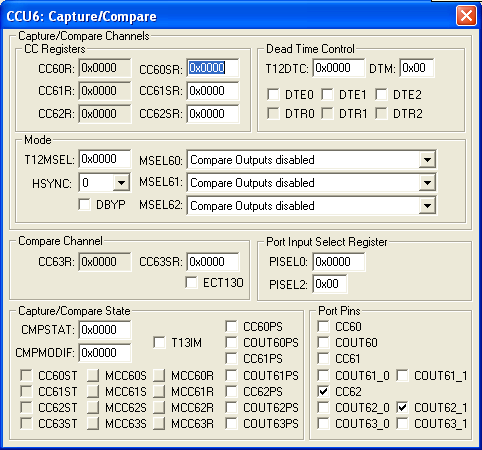

CCU6 Capture Compare Dialog

The CCU6: Capture/Compare Dialog controls the compare and capture functions. The compare function generates an output signal when a compare timer equals a preset value. The capture function stores a capture timer value based on an external signal.

Capture/Compare Channels

- CC6xR (Capture/Compare Registers 0-2) are read-only registers that hold the target compare or capture values.

- CC6xSR (Capture/Compare Shadow Registers 0-2) contain the next value to be stored by the CCU into CC6xR.

Dead Time Control

- T12DTC (Timer T12 Dead-Time Control Register) contains the dead-time control bit setting below:

- DTM (Dead-Time) is an 8-bit down count that defines the delay between passive to active states for the Timer 12 compare channel.

- DTEx (Dead-Time Enable Bits) are set to allow dead-time generation for each capture/compare channel (0-2).

- DTRx (Dead-Time Run Indication Bits) are set when a dead-time counter is non-zero.

Mode

- T12MSELx (T12 Capture/Compare Mode Select Register) contains the MSEL6x bits described below.

- MSEL6x (Capture/Compare Mode Select Register 0-2) selects one of the capture or compare operating modes.

Compare Channel

- CC63R (Capture/Compare Registers for Channel 63) are read-only registers that hold the target compare values compared to Timer 13.

- CC63SR (Capture/Compare Shadow Registers for Channel 63) contain the next value to be stored by the CCU into CC63R.

Port Input Select Register

- PISEL0 (Port Input Select Register 0) contains the port input pin selection definitions for capture modules CC60-CC62 and CCPOS0-CCPOS2.

- PISEL2 (Port Input Select Register 2) contains the port input pin selection definitions for input signals T13HR_0-T13HR_2.

Capture/Compare State

- CMPSTAT (Compare State Register) contains the CC6xST, CC6xPS and COUT6xPS state bits defined below.

- CMPMODIF (Compare State Register) contains the MCC6xS and MCC6xR state bits defined below.

- CC6xST (Capture/Compare State Bits) show the state of the compare/capture channels. When set in compare mode, the counter value is greater than or equal to the compare value. When set in capture mode, the selected edge has been detected.

- MCC6xS and MCC6xR (Capture/Compare Status Modification Bits) are used to change output line status by setting (using MCC6xS) or resetting (using MCC6xR) the CC6xST bits.

- CC6xPS and COUT6xPS (Passive State Select for Compare Outputs)

- when set, the compare output drives the passive level when CC6xST is set.

Port Pins Group

- CC6x and COUT6x (Capture Compare Channel CC60-CC62 Input/Output) displays or sets the Capture Compare I/O Channel pins CC60-CC62 (P3.0, P3.2 and P3.4), COUT60-COUT63 (P3.1, P3.3, P3.5 and P3.7) and COUT61_1-COUT63_1 (P0.1, P0.5 and P0.3).

CCU6 Modulation Dialog

The CCU6: Modulation Dialog provides modulation, trap and multi-channel output control for the Compare/Capture Unit.

Modulation Control

- MODCTR (Capture Compare Registers 0-2) holds the target compare or capture values.

- MCMEN (Multi-Channel Mode Enable) enables a multi-channel pattern modulation.

- ECT13Ox (Enable Compare Timer T13 Output) enables the alternate output function of COUT63 for the Timer 13 PWM signal.

- T12MODENx (T12 Modulation Enable) enables modulation of the CC60-CC62 and COUT60-COUT62 pins by a Timer 12 PWM signal.

- T13MODENx (T13 Modulation Enable) enables modulation of the CC60-CC62 and COUT60-COUT62 pins by a Timer 13 PWM signal.

Trap Control

- TRPCTR (Trap Control Register) contains trap control bit settings below.

- TRPM0-TRPM1 (Trap Mode Control Bits 0 and 1) defines whether the trap state synchronizes with Timer 12, Timer 13 or neither, when the trap becomes inactive.

- TRPM2 (Trap Mode Control Bit 2) is set to return the trap state to normal when the TRPF bit is set after CTRAP# goes inactive. Otherwise, the trap state returns to normal immediately after CTRAP# goes inactive.

- TRPEN13 (Trap Enable Control for Timer 13) if set, the Timer 13 PWM output state is passive while TRPS is set.

- TRPPEN (Trap Pin Enable) enabled trapping based on the CTRAP# pin.

- CTRAP# (External Emergency Stop Pin) provides a fast emergency MCU stop from an external source.

- TRPEN.x (Trap Enable Control) enables the trap function for CC60-CC62 and COUT60-COUT62 pins. Passive state is controlled by TRPS.

Passive State Level

- PSLR (Passive State Level Register) contains the PSL.x and PSL63 bit defined below.

- PSL.x (Compare Outputs Passive State Level) defines the passive level of pins CC60-CC62 and COUT60-COUT62 during the passive state.

- PSL63 (Passive State Level of Output COUT63) defines the passive level of pins COUT63 during the passive state.

Multi Channel Output

- MCMOUTS (Multi-Channel Mode Output Shadow Register) contains the following settings:

- STRMCM (Shadow Transfer Request for MCMPS) is set to force the shadow register (MCMPS) to update MCMP.

- STRHP (Shadow Transfer Request for the Hall Pattern) is set to force the Hall pattern shadow registers (CURHS and EXPHS) to update the current Hall pattern registers (CURH and EXPH), respectively.

- EXPHSx (Expected Hall Pattern Shadow) contains the shadow bit filed for EXPH.

- CURHSx (Current Hall Pattern Shadow) contains the shadow bit filed for CURH.

- MCMOUT (Multi-Channel Mode Output Register) contains the value to be updated to MCMP on the next shadow transfer.

- R (Reminder Flag) is set when a trigger source requests a shadow transfer from MCMPS to MCMP, but the selected synchronization has not occurred.

- MCMPx (Multi-Channel PWM Pattern) allows Timer 12 or 13 to generate the PWM signal to pins CC60-CC62 and COUT60-COUT62.

- EXPHx (Expected Hall Pattern) is compared to the Current Hall Pattern(CURH) and sets the Correct Hall Event bit(CHE) if they match. If they do not match, the Wrong Hall Event(WHE) bit is set and generates an error interrupt if ENWHE is set.

- CURHx (Current Hall Pattern) is compared to the hall input pins

Hall Sensors

- CCPOSx (Sampled Hall Pattern Bits) indicate the last Hall pattern compared to the current and expected Hall Pattern values(CURH and EXPH).

Multi-Channel Output

- MCMCTR (Multi-Channel Mode Control Register) contains the following settings:

- SWSEL (Switching Selection) selects the trigger source for the shadow transfer from MCMPS to MCMP.

- SWSYN (Switching Synchronization) triggers a shadow transfer from MCMPS to MCMP if the Reminder Flag (R) is set.

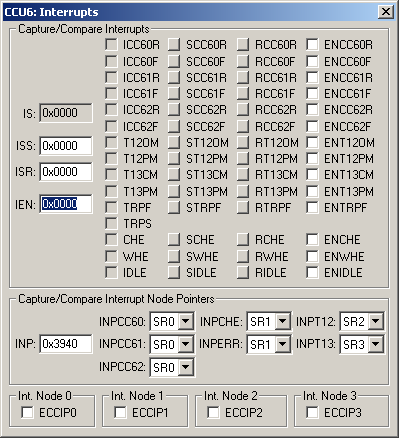

CCU6: Interrupts Dialog

The CCU6: Interrupts Dialog provides interrupt control for the Capture/Compare Unit.

Compare/Capture Interrupts

- IS (Capture/Compare Interrupt Status Register) contains the following bits:

- IIC6xR (Capture, Compare-Match Rising Edge Flag) is set when a Timer 12 match is detected while counting up in compare mode, or when a rising edge of CC6x is detected in capture mode.

- IIC6xF (Capture, Compare-Match Falling Edge Flag) is set when a Timer 12 match is detected while counting down in compare mode, or when a falling edge of CC6x is detected in capture mode.

- T12OM (Timer T12 One-Match Flag) is set when a Timer 12 one-match while counting down is detected.

- T12PM (Timer T12 Period-Match Flag) is set when a Timer 12 period-match while counting up is detected.

- T13CM (Timer T13 Compare-Match Flag) is set when a Timer 13 compare-match is detected.

- T13PM (Timer T13 Period-Match Flag) is set when a Timer 13 period-match is detected.

- TRPF (Trap Flag) is set when the CTRAP# is triggered.

- TRPS (Trap State) is set when the trap state is active.

- CHE (Correct Hall Event) is set when an expected hall event is detected.

- WHE (Wrong Hall Event) is set when the expected hall event is different from the last hall event input.

- IDLE (Idle State) is set when the CCU is in a passive state and the MCMP is cleared.

- ISS (Capture/Compare Interrupt Status Set Register) contains the following bits:

- SCC6xR sets the Capture, Compare-Match Rising Edge Flag(IIC6xR).

- SCC6xF sets the Capture, Compare-Match Falling Edge Flag(IIC6xF).

- ST12OM sets the Timer T12 One-Match Flag(T12OM).

- ST12PM sets the Timer T12 Period-Match Flag(T12OM).

- ST13CM sets the Timer T13 Compare-Match Flag(T13CM).

- ST13PM sets the (Timer T13 Period-Match Flag)

- STRPF sets the Trap Flag(TRPF).

- SCHE sets the Correct Hall Event Flag(CHE).

- SWHE sets the Wrong Hall Event Flag(WHE).

- SIDLE sets the Idle State Flag(IDLE).

- ISR (Capture/Compare Interrupt Status Reset Register) contains the following bits:

- RT12OM resets the Timer T12 One-Match Flag(T12OM).

- RT12PM resets the Timer T12 Period-Match Flag(T12OM).

- RT13CM resets the Timer T13 Compare-Match Flag(T13CM).

- RT13PM resets the (Timer T13 Period-Match Flag)

- RTRPF resets the Trap Flag(TRPF).

- RCHE resets the Correct Hall Event Flag(CHE).

- RWHE resets the Wrong Hall Event Flag(WHE).

- RIDLE resets the Idle State Flag(IDLE).

- IEN (Capture/Compare Interrupt Enable Register) contains the following bits:

- ENCC6xR enables the Capture, Compare-Match Rising Edge Interrupt.

- ENCC6xF enables the Capture, Compare-Match Falling Edge Interrupt.

- ENT12OM enables the Timer T12 One-Match Interrupt.

- ENT12PM enables the Timer T12 Period-Match Interrupt.

- ENT13CM enables the Timer T13 Compare-Match Interrupt.

- ENT13PM enables the Timer T13 Period-Match Interrupt.

- ENTRPF enables the Trap Interrupt.

- ENCHE enables the Correct Hall Event Interrupt.

- ENWHE enables the Wrong Hall Event Interrupt.

- ENIDLE enables the Idle State Interrupt.

Capture/Compare Interrupt Node Pointers

- INP (Capture/Compare Interrupt Node Pointer Register) contains the following:

- INPCC6x (Node Pointer for Channel 0-2 Interrupts) selects the interrupt output line (SR0-SR3) that is active when ICC6xR or ICC6xF bits are set.

- INPCHE (Node Pointer for the CHE Interrupt) selects the interrupt output line (SR0-SR3) that is active when CHE bit is set.

- INPERR (Node Pointer for Error Interrupts) selects the interrupt output line (SR0-SR3) that is active when WHE or TRPF bit is set.

- INPT12 (Node Pointer for Timer T12 Interrupts) selects the interrupt output line (SR0-SR3) that is active when T12OM bit is set.

- INPT13 (Node Pointer for Timer T13 Interrupts) selects the interrupt output line (SR0-SR3) that is active when T13PM bit is set.

Int Node x

- ECCIPx (CCU6 Interrupt Node Pointer 0-3 Enable) is set when interrupt node pointer 0-3 is enabled

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |