|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC2102 — I�C Interface

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

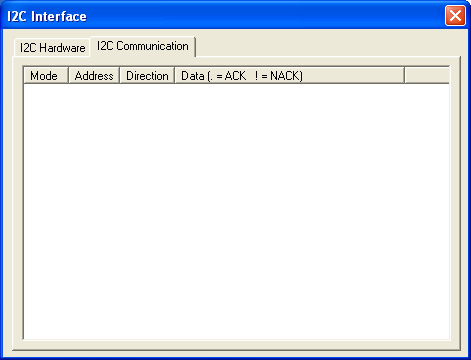

I2C Communication Dialog

The I2C Communication dialog displays the I2C communication activity on the I2C bus. The message Mode, Address, Direction and data message content are displayed for each message. To clear the message display, double-click anywhere in the message display area.

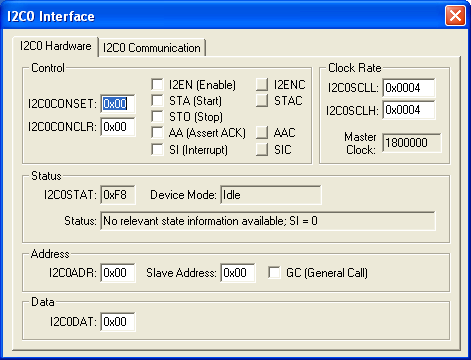

I2C Hardware Dialog

The I2C Hardware dialog configures one of the on-chip I2C controllers. Each I2C controller fully supports master or slave operations. The following groups control the simulation of the I2C Interfaces:

I2C Control Group

- I2CnCONSET (I2C Control Set Register) is used to set bits in the I2C control register. A bit value of zero in this register has no effect on the I2C control register. It contains the following control bits:

- I2EN (Enable) is set to enable this I2C interface.

- STA (Start) is set to enter master mode and send a START condition.

- STO (Stop) is set to send a STOP condition in master mode, and recover from an error in slave mode.

- AA (Assert ACK) is set to request an acknowledge be returned from the slave device.

- SI (Interrupt) is set to indicate a state change in the I2C controller.

- I2CnCONCLR (I2C Control Clear Register) is used to clear bits in the I2C control register. A bit value of zero in this register has no effect on the I2C control register. It contains the following control bits:

- I2ENC disables the I2C controller.

- STAC clears the START flag.

- AAC clears the Assert ACK flag.

- SIC clears the I2C interrupt flag.

Clock Rate Group

- I2CnSCLL (I2C SCL Low Duty Cycle Register) contains the SCL Low Duty Cycle count.

- I2CnSCLH (I2C SCL High Duty Cycle Register) contains the SCL High Duty Cycle count.

- Master Clock displays the serial clock.

Status Group

- I2CnSTAT (Slave Status Register) contains I2C interface status code. The Device Mode and Status display a decoded description of the interface status register value.

Address Group

- I2CnADR (I2C Slave Address Register) contains the value of the I2C slave address register. This register is only valid in Slave mode.

- Device Address contains the slave device address.

- GC is set to respond to a General Call address(0x00).

Data Group

- I2CnDAT contains the data byte to be sent or the last data byte received.

I2C0_IN VTREG

Data Type: unsigned short

I2C0_OUT VTREG

Data Type: unsigned short

I2C1_IN VTREG

Data Type: unsigned short

I2C1_OUT VTREG

Data Type: unsigned short

I2C2 Input VTREG

Data Type: unsigned short

I2C2 Output VTREG

Data Type: unsigned short

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |