|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For STMicroelectronics STR710FZ2 — Real Time Clock (RTC)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

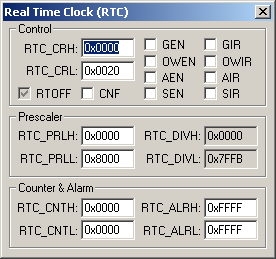

Real Time Clock Dialog

The Real Time Clock Dialog shows the current state of the on-chip real-time clock (RTC). You can change the RTC settings using the controls in this dialog.

Control

- RTC_CRH (RTC Control Register High) contains the bit used to mask Global, Overflow, Alarm and Second Interrupt requests.

- GEN (Global Interrupt Enable) is set enable global interrupts.

- OWEN (Overflow Interrupt Enable) is set enable overflow interrupts.

- AEN (Alarm Interrupt Enable) is set enable alarm interrupts.

- SEN (Second Interrupt Enable) is set enable second interrupts.

- RTC_CRL (RTC Control Register Low) contains the following bit settings:

- RTOFF (RTC operation OFF) is set when the last write operation to the RTC registers completes.

- CNF (Configuration Flag) is set enter configuration mode to allow new values to be written to RTC_CNT, RTC_ALR or RTC_PRL registers.

- GIR (Global Interrupt Request) is set when a global interrupt request is pending.

- OWIR (Overflow Interrupt Request) is set when a overflow interrupt request is pending.

- AIR (Alarm Interrupt Request) is set when a alarm interrupt request is pending.

- SIR (Second Interrupt Request) is set when a second interrupt request is pending.

Prescaler

- RTC_PRLH (RTC Prescaler Load Register High) contains the 4 high-order bits of the RTC prescaler reload value.

- RTC_PRLL (RTC Prescaler Load Register Low) contains the 16 low-order bits of the RTC prescaler reload value.

- RTC_DIVH (RTC Clock Divider High) contains the 4 high-order bits of the RTC clock divider.

- RTC_DIVL (RTC Clock Divider Low) contains the 16 low-order bits of the RTC clock divider.

Counter & Alarm

- RTC_CNTH (RTC Counter Register High) contains the 16 high-order bits of the RTC counter register.

- RTC_CNTL (RTC Counter Register Low) contains the 16 low-order bits of the RTC counter register.

- RTC_ALRH (RTC Alarm Register High) contains the 16 high-order bits of the RTC alarm register .

- RTC_ALRL (RTC Alarm Register Low) contains the 16 low-order bits of the RTC alarm register.

Real Time Clock Input VTREG

Data Type: unsigned long

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |