|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For STMicroelectronics ST10F273E — CPU with System Configuration

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

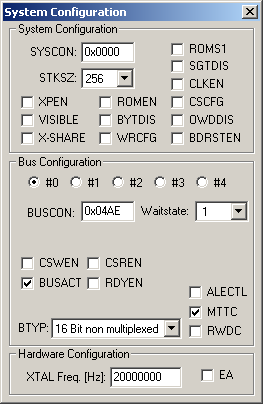

System Configuration Dialog

The System Configuration dialog displays and allows you to edit the system, bus, and hardware configuration options.

The System Configuration group contains the following controls.

- SYSCON is the System Configuration Register (SFR).

- STKSZ specifies the size of the system stack.

- XPEN enables access to the on-chip XBUS peripherals (when checked).

- VISIBLE specifies that XBUS peripheral accesses are visible on the external pins (when checked).

- X-SHARE specifies that XBUS peripherals are accessible on the external bus during HOLD mode (when checked).

- ROMEN enables the internal program ROM (when checked).

- BYTDIS disables BHE pin (when checked).

- WRCFG enables alternale function for WR and BHE pins. WR acts as WRL and BHE acts as WRH (when checked).

- ROMS1 maps internal ROM to segment 0x01 (when checked).

- SGTDIS disables segmentation (when checked).

- CLKEN enables the system clock output (when checked).

- CSCFG enables unlatched CS mode (when checked).

- OWDDIS disables the oscillator watchdog timer (when checked).

- BDRSTEN is the Bidirectional Reset Enable Bit.

The Bus Configuration group contains the following controls.

- #0-#4 selects the BUSCON register to view/change.

- BUSCON contains the value of the BUSCON Register (SFR).

- ADDRSEL contains the value of the ADDRSEL Register (SFR) for BUSCON1-BUSCON4.

- Waitstate specifies the number of waitstates for BUSCON0-BUSCON4.

- Range specifies the address range for BUSCON1-BUSCON4.

- Start lists the starting address for BUSCON1-BUSCON4

- CSWEN generates CS signal for the duration of a write command (when checked).

- BUSACT enables the external bus for the specifies address space (when checked).

- CSREN generates CS signal for the duration of a read command (when checked).

- RDYEN enables external bus cycle control via READY input (when checked).

- BTYP selects the external bus configuration.

- ALECTL lengthens the ALE signal (when checked).

- MTTC disables 1 waitstate for memory tristate (when checked).

- RWDC disables the read/write timing delay (when checked).

The Hardware Configuration group contains the following controls.

- XTAL Freq. specifies the external oscillator frequency.

- EA is the state of the EA pin.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |