|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Analog Devices ADuC7026 — PLL & Oscillator and Power Control

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

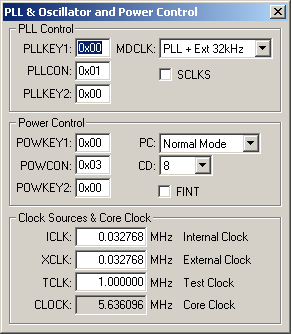

PLL & Oscillator and Power Control Dialog

The PLL & Oscillator and Power Control Dialog controls the phase-locked loop, oscillator and power saving mode of the ARM controller. With this dialog, you control the internal and external clocking and change clock speed to conserve power.

PLL Control Group

- PLLKEY1 contains the preamble key value (0xAA) used in conjuction with writing the PLLCON register.

- PLLCON (PLL Control Register) contains the SCLKS and MDCLK configuration values.

- PLLKEY2 contains the postamble key value (0x55) used in conjuction with writing the PLLCON register.

- MDCLK (Clocking Mode) selects the clocking mode (VCO, PLL + External 32kHz crystal, XCLKI pin 36 or XCLK pin 17) from a drop-down list.

- SCLKS (Slow Clock Select) is set to use the internal 32kHz clock for the timer. It is reset to use an external 32kHz crystal.

Power Control Group

- POWKEY1 contains the preamble key value (0x01) used in conjuction with writing the POWCON register.

- POWCON (Power Control Register) contains the power control settings PC CD and FINT.

- POWKEY2 contains the postamble key value (0xF4) used in conjuction with writing the POWCON register.

- PC (Power Control) selects Normal or Power Down mode.

- CD (CPU Clock Divider) selects the clock divider value (1, 2, 4, 8, 16, 32, 64 or 128).

- FINT (Fast Interrupt Response) is set to enable fast interrupt repose. This allows the CPU to run at the fastest clock rate while executing an interrupt service routine.

Clock Sources & Core Clock Group

- ICLK contains the internal clock rate.

- XCLK contains the external clock rate.

- TCLK contains the test clock rate.

- CLOCK displays the core clock rate.

CLOCK VTREG

Data Type: unsigned long

The CLOCK VTREG contains the speed of the microcontroller instruction clock (in Hertz). This is effectively the number of 1-cycle instructions that the simulated microcontroller can execute each second. This number is derived by dividing the oscillator frequency (specified by the XCLK VTREG) by a fixed number. CLOCK is a read-only VTREG. It may not be changed directly. It changes when the value of the XCLK VTREG or the clock divisor (which is not available on all devices) changes.

ICLK VTREG

Data Type: unsigned long

Internal Clock Input

XCLK VTREG

Data Type: unsigned long

The XCLK VTREG contains the frequency of the external oscillator (in Hertz) used to drive the microcontroller. The value is automatically set from the value specified in Project Options - Options for Target. However, you may change the value of XCLK using the command window. For example:

XCLK=33000000

You may also output the current value of XCLK using the following:

XCLK

XCLK may be used in calculations to synchronize external scripts with the simulated microcontroller.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |