|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) P89LPC935 — CCU (Compare/Capture Unit)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

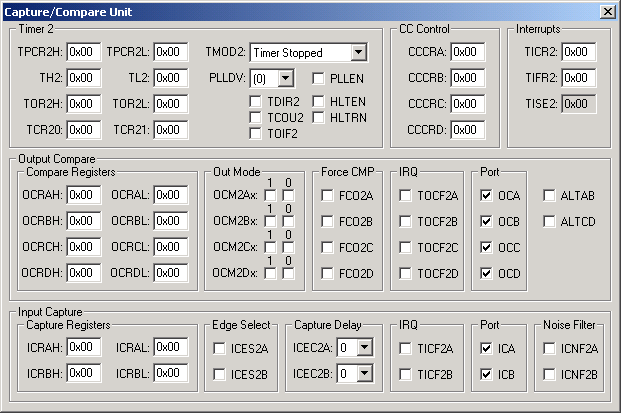

Capture/Compare Unit Dialog

The Capture Compare Unit (CCU) Dialog controls the compare and capture functions. The compare function generates an output signal when a compare timer equals a preset value. The capture function stores a capture timer value based on an external signal.

Timer 2 Group

- TPCR2H (CCU Prescaler Control Register High) contains the upper 2 bits of the 10-bit prescaler value.

- TPCR2L (CCU Prescaler Control Register Low) contains the lower 8 bits of the 10-bit prescaler value.

- TH2 (Timer 2 High Byte) contains the Timer 2 MSB.

- TL2 (Timer 2 Low Byte) contains the Timer 2 LSB.

- TOR2H (CCU Reload Register High) is the MSB of the overflow reload value.

- TOR2L (CCU Reload Register Low) is the LSB of the overflow reload value.

- TCR20 (CCU Control Register 0) contains the PLLEN, HLTRN, HLTEN and TDIR2 settings below.

- TCR21 (CCU Control Register 1) contains the TCOU2 and the PLLDV settings.

- TMOD2 (CCU Timer Mode Select) selects Basic, Synchronous PWM or Asynchronous PWM timer mode.

- PLLDV (PLL Frequency Divisor) selects the value that is divided into PCLK to produce the PLL frequency.

- PLLEN (Phase Locked Loop Enable) is set to start a PLL operation.

- TDIR2 (CCU Timer Count Direction) is set to count down and reset to count up.

- TCOU2 (CCU Timer Compare/Overflow Update) is set to move the contents of the shadow registers into TOR2H and TOR2L. This is moved immediately in Basic Timer mode or on the next CCU Timer overflow in PWM mode.

- TOIF2 (CCU Timer Overflow Interrupt Flag) is set when a CCU Timer reload occurs.

- HLTEN (PWM Halt Enable) is set to capture stop all capture activity on the PWM pins.

- HLTRN (PWM Halt) is set when a PWM Halt occurs.

CC Control Group

- CCCRx (Capture Compare Control Register x) contains the ICECx, the ICESx, the ICESx and the FCOx settings described below.

Interrupts Group

- TICR2 (CCU Interrupt Control Register) contains the CCU Timer Overflow Interrupt Enable (TOIE2) and the Output Compare Channel Interrupt Enable (TOCIE2) settings.

- TIFR2 (CCU Interrupt Flag Register) contains the CCU Timer Overflow Interrupt Flag (TOIF2), Output Compare Channel Interrupt Flag (TOCF2) and Input Capture Channel Interrupt Flag (TICF2) settings.

- TISE2 (CCU Interrupt Status Encode Register) contains the CCU Interrupt Encode Output (ENCINT) setting.

Output Compare Registers Group

- OCRxH (Output Compare Channel x High Byte) is MSB of output compare channel x. The contents of T2H are compared to this value and trigger an interrupt if these values match and the OCRxL and T2L values match.

- OCRxL (Output Compare Channel x Low Byte) is LSB of output compare channel x. The contents of T2L are compared to this value and trigger an interrupt if these values match and the OCRxH and T2H values match.

Out Mode Group

- OCMx0 and OCMx0 (Output Compare Mode x) enables and selects the output compare pin behavior based on the CCU Timer Mode Select setting (TMOD2). These setting control whether Basic mode sets or toggles the Output Compare pin. PWM modes will clear the Output Compare bit for Inverted, Asynchronous PWM and Non-inverted, Synchronous PWM and set the Output Compare bit for Inverted, Synchronous PWM and Non-inverted, Asynchronous PWM.

Force CMP Group

- FCOx (Force Compare x Output) is set forces a compare condition for channel x.

IRQ Group

- TOCF2x (Output Compare Channel x Interrupt Flag) is set when the contents of TH2 and TL2 match that of OCRHx and OCRLx.

Port Group

- OCx (Output Compare x) is the signal level on the CCU output pin for channel x.

- ALTAB (Alternate PWM Channels A and B) is set to alternately gate the output of channels A and B on each counter cycle.

- ALTCD (Alternate PWM Channels C and D) is set to alternately gate the output of channels C and D on each counter cycle.

Input Capture Registers Group

- ICRAH (Input Capture Register High) contains the MSB of the 16-bit Input capture register A.

- ICRAL (Input Capture Register Low) contains the LSB of the 16-bit Input capture register A.

- ICRBH (Input Capture Register High) contains the MSB of the 16-bit Input capture register B.

- ICRBL (Input Capture Register Low) contains the LSB of the 16-bit Input capture register B.

Input Edge Select Group

- ICESA (Input Capture A Edge Select Bit) is set to trigger an input capture event for channel A on a rising edge and reset to trigger on a falling edge.

- ICESB (Input Capture B Edge Select Bit) is set to trigger an input capture event for channel A on a rising edge and reset to trigger on a falling edge.

Input Capture Delay Group

- ICECA (Capture Delay Setting A) contains the number of clock edges to delay before an input capture occurs on channel A.

- ICECB (Capture Delay Setting B) contains the number of clock edges to delay before an input capture occurs on channel B.

Input IRQ Group

- TICF2A (Input Capture Channel A Interrupt Flag) is set when an input capture event occurs for channel A.

- TICF2B (Input Capture Channel B Interrupt Flag) is set when an input capture event occurs for channel B.

Input Port Group

- ICA (Input Capture A) is the input port pin for channel A capture.

- ICB (Input Capture B) is the input port pin for channel B capture.

Noise Filter Group

- ICNFA (Input Capture Noise Filter A) is set to require 4 consecutive sample of the same value before declaring a capture event on channel A.

- ICNFB (Input Capture Noise Filter B) is set to require 4 consecutive sample of the same value before declaring a capture event on channel B.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |