|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC2124 — UART 0

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

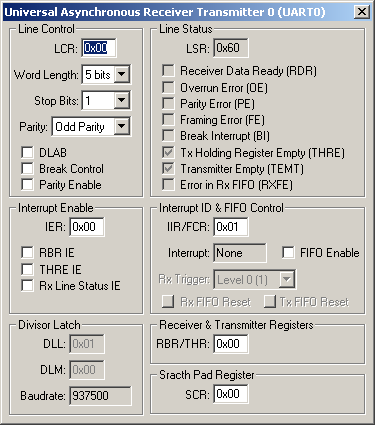

UART 0 Dialog

The Universal Asynchronous Receiver Transmitter (UART 0) Dialog configures UART 0. A UART transfers serial data to and from external devices and the ARM controller. The UART can be configured in a variety of ways to suit the external serial device.

Line Control Group

- LCR (Line Control Register) displays the combined control information for the following:

- Word Length selects the data character length of 5, 6, 7 or 8 bits per character.

- Stop Bits (Number of Stop Bits) selects the number of stop bits to be sent with each character.

- Parity selects odd, even or no (forced "0" or "1") parity.

- DLAB (Divisor Latch Access Bit) is set to calculate the baud rate based on the Divisor Latch register (DLL and DLM) values.

- Break Control is set to enable transmission of a Break.

- Parity Enable is set to enable parity generation and checking.

Line Status Group

- Receiver Data Ready (RDR) set when the UART 0 receives at least 1 character and the receiver hold register is not empty.

- Overrun Error (OE) set if the controller detects an overrun condition since the last status reset command.

- Parity Error (PE) set if the controller detects at least 1 false parity bit since the last status reset command.

- Framing Error (FE) set if the controller detects a framing error since the last status reset command.

- Break Interrupt (BI) is set when a Break condition occurs while receiving data.

- Tx Holding Register Empty (THRE) is set when the transmission hold register is empty.

- Transmitter Empty (TEMT) set if there are no characters in the transmitter.

- Error in Rx FIFO (RXFE) is set when the receiver detects any error (parity, framing, overrun or break).

Interrupt Enable Group

- IER (Interrupt Enable Register) contains the RBR, THRE and Line Status Enable bits.

- RBR IE (Receive Buffer Register Interrupt Enable) is set to enable the Receive Data Available interrupt.

- THRE IE (Transmit Hold Register Empty Interrupt Enable) is set to enable the Transmitter Empty (THRE) interrupt.

- Rx Line Status EI (Line Status Interrrupt Enable) is set to enable Line Status interrupts.

Interrupt ID & FIFO Control Group

- IIR/FCR (Interrupt Identification/FIFO Control Register)

- Interrupt displays the interrupt type(Line Status, THRE, RDA, Character Time-out).

- FIFO Enable (FIFO Enable) is set to clear and enable the receive and transmit FIFOs.

- Rx Trigger (Rx Trigger Level Select) sets the number of characters required to trigger a receive interrupt.

- Rx FIFO Reset clears the receive FIFO buffer.

- Tx FIFO Reset clears the transmit FIFO buffer.

Divisor Latch Group

- DLL (Divisor Latch LSB Register) contains the lower 8-bit value that the MCU divides into the MCU clock (PCLK) to generate the UART baud rate.

- DLM (Divisor Latch MSB Register) contains the upper 8-bit value that the MCU divides into the MCU clock (PCLK) to generate the UART baud rate.

- Baudrate is the computed UART baud rate.

Receiver & Transmitter Registers Group

- RBR/THR (Receiver Buffer Register/Transmitter Hold Register) when receiving, is the oldest character received. When transmitting, it is the newest character to be transmitted.

Scratch Pad Group

- SCR (Scratch Pad Register) has no effect on the UART operation. It can be used for general purpose storage.

SxIN VTREG

Data Type: unsigned int

The SxIN VTREG represents the serial input of the simulated microcontroller. Values you assign to SxIN are input to the serial channel 0, 1, 2, and so on. You may assign input using the command window. For example,

S0IN='A'

causes the simulated microcontroller serial input 0 to receive the ASCII character A. If you want to use the SxIN VRTEG to simulate reception of multiple characters, you must be sure to delay for at least one character time between successive assignments to SxIN. This may be done using a signal function. For example:

signal void send_cat (void) {

swatch(0.01); /* Wait 1/100 seconds */

S0IN='C'; /* Send a C */

swatch(0.01);

S0IN='A';

swatch(0.01);

S0IN='T';

}

You may use the SxIN VTREG to input data (5-8 bits), parity, frame error and break condition. SxIN Format (16-bit Register)

- Bits 0-7: Data (5, 6, 7, or 8 bit)

- Bit 8: Parity bit Value

- Bit 9: Parity bit Presence (0=Not present, 1=Present)

- Bit 10: Invalid Stop bit (0=Normal, 1=Invalid)

For example:

S0IN=0x0074 // Data = 0x74, No Parity bit

S0IN=0x0274 // Data = 0x74, Parity bit = 0

S0IN=0x0374 // Data = 0x74, Parity bit = 1

S0IN=0x0474 // Data = 0x74, No Parity bit

// Invalid Stop bit - Frame Error

S0IN=0x0400 // Break Condintion

In addition to the SxIN VRTEG, the serial window allows you to input serial characters by simply typing. Serial characters that are transmitted byt the simulated microcontroller appear in the serial window.

SxOUT VTREG

Data Type: unsigned int

The SxOUT VTREG represents the serial output from the simulated serial port 0, 1, and so on. Whenever the simulated serial port transmits a character, the value transmitted is automatically assigned to SxOUT (which is read-only). You may read the value of SxOUT to determine the character transmitted by your simulated program. For example,

S0OUT

outputs the value of the last character transmitted by serial port 0.

SxOUT Format (16-bit Register)

- Bits 0-7: Data (5, 6, 7, or 8 bits)

- Bit 8: Parity bit Value

- Bit 9: Parity bit Presence (0=Not present, 1=Present)

- Bit 10: Invalid Stop bit (0=Normal, 1=Invalid)

For example:

S0OUT & 0x00FF // Data S0OUT & 0x0200 // Parity bit is present S0OUT & 0x0100 // Parity bit value (0=0, 0x0200=1)

Note that you cannot assign values to the SxOUT VTREGs. You may use the SxOUT VTREG in a script to process transmitted data. For example,

signal void s0out_sig (void) {

while (1)

{

wwatch(S0OUT); /* wait for something in S0OUT */

printf ("Transmitted a %2.2X\n", (unsigned) S0OUT);

}

}

SxTIME VTREG

Data Type: unsigned char

The SxTIME VTREG allows you to control the timing of the simulated serial port 0, 1, and so on.

- A value of 1 (which is the default) indicates that the serial port timing is identical to the target hardware. Use this value when you want to see the effects of baud rate on the serial port I/O.

- A value of 0 indicates that all serial input and output occur instantaneously. Use this value when you don't care about any baud rate effects or when you want serial output to be fast.

For example:

S0TIME = 0 /* Set Serial Port 0 for FAST timing */ S0TIME = 1 /* Set Serial Port 0 for accurate timing */

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |