|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Atmel AT91FR40162 — External Bus Interface

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

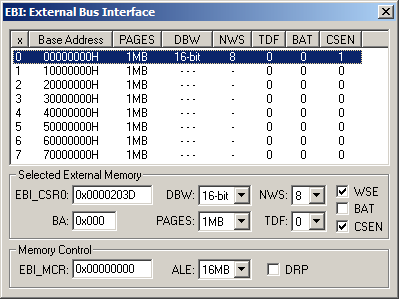

Exernal Bus Interface Dialog

The External Bus Interface Dialog controls bus access and chip selects for up to 8 external memory or peripheral devices. The base address, page size, bus width, wait states, and bus access type settings for each chip select are displayed at the top of the dialog. Once selected, a chip select is configured using the following controls:

Selected External Memory

- EBI_CSRx (Chip Select Register) displays the configuration of the selected chip select. It contains the settings of the following controls:

- BA (Base Address) contains the most significant bits of the base address. The number of bits in BA changes based on the value of PAGES.

- DBW (Data Bus Width) is set to 8 or 16-bits.

- PAGES selects the memory page size of 1, 4, 16 or 64 megabytes.

- NWS (Number Wait States) sets the number of wait states inserted during an access to the corresponding chip select.

- TDF (Data Float Output Time) contains the number of wait states for slow memory devices. TDF delays do not affect internal memory accesses.

- WSE (Wait-State Enable) enables NWS wait states (when checked).

- BAT (Byte Access Type) enables byte-select access when checked. BAT enables byte-write access when not checked.

- CSEN enables this chip select when checked.

Memory Control

- EBI_MCR (Memory Control Register) selects the chip select and memory address lines. It contains the ALE and DRP settings below:

- ALE (Address Line Enable) controls the combination of valid address lines and valid chip select lines for addressing memory.

- DRP (Data Read Protocol) enables early read protocol for external memory devices when checked. Standard read protocol is used when not checked.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |