|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Atmel AT91FR40162 — Power Saving

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

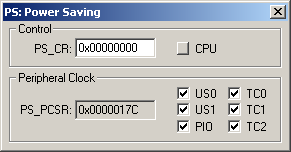

Power Saving Dialog

The Power Saving Dialog controls the power saving mode of the ARM controller. Pressing the CPU button stops the ARM7TDMI clock and forces the processor into Idle mode. The PS_CR (Power Saving Control Register) is a write-only register. The CPU button uses this register to disable the CPU clock.

Peripheral Clock

- PC_PCSR (Peripheral Clock Status Register) displays the current status of the peripheral clock.

- US0 if set, enables the USART 0 clock.

- US1 if set, enables the USART 1 clock.

- PIO if set, enables the parallel I/O clock.

- TC0 if set, enables the Timer/Counter 0 clock.

- TC1 if set, enables the Timer/Counter 1 clock.

- TC2 if set, enables the Timer/Counter 2 clock.

WAKEUP VTREG

Data Type: unsigned char

THE WAKEUP VTREG contains the state of the WAKEUP pin on the simulated MCU.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |