|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Silicon Laboratories, Inc. C8051F002 — SPI Interface

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

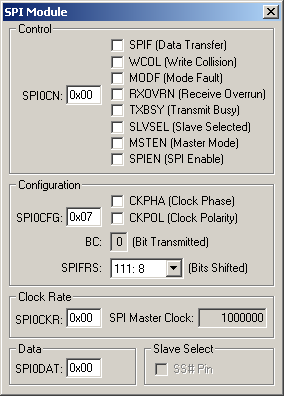

Serial Peripheral Interface Dialog

The Serial Peripheral Interface Dialog allows you to view and edit the Serial Peripheral Interface (SPI) simulator configuration. Simulation of this interface is controlled by the following groups:

Control

- SPIOCN (Serial Peripheral Control Register) contains the following bits that control the functions of the SPI:

- SPIF (Data Transfer) is set when the SPI completes a data transfer operation. This bit clears after this register and the data register (SPIODAT) are read.

- WCOL (Write Collision) is set when data is written to the SPI data register while a SPI data transfer is in progress.

- MODF (Mode Fault) is set when the slave select signal(NSS) goes low and the SPI is configured as a Master.

- RXOVRN (Receive Overrun) is set when the SPI receives data before it's read buffer is empty.

- TXBSY (Transmit Busy) is set when the SPI receives data before its read buffer is empty.

- SLVSEL (Slave Selected) is set in multi-master environments to indicate that this module is selected by another device as a slave.

- MSTEN (Master Mode) is set to configure the SPI as a Master.

- SPIEN (SPI Interrupt Enable) is set to enable SPI interrupts.

Configuration

- SPIOCFG (SPI Configuration Register) contains the following settings:

- CKPHA (Clock Phase) is set to sample data on the second edge of the SCK period

- CKPOL (Clock Polarity) is set when the serial clock (SCK) is active high. If reset, SCK is active low.

- BC (Bit Transmitted) displays the bit transmitted.

- SPIFRS (Frame Size) in master mode, contains the number of bits to shift in or out of the shift register during data transfer.

Clock Rate

- SPIOCKR (SPI Clock Counter Register) controls the SPI clock rate when the SPI is configured as a master.

- SPI Master Clock is the SPI clock value (SCK) based on the SPIOCKR setting.

Data

- SPIODAT (SPI Data Register) contains the either the data to be transmitted or the data received. In Master mode, writing to this register starts data transfer.

Slave Select

- SS# Pin (Slave Select) is the signal level at the slave select pin.

SPI_IN VTREG

Data Type: unsigned int

The SPI_IN VTREG contains a byte which is received via the MCU SPI (Serial Peripheral Interface) port on the next SPI transfer. You may use this VTREG in a simulation script. For example:

signal void spi_func (void) {

while (1) {

wwatch (SPI_OUT);

printf ("SPI_OUT: %2.2X\n", (unsigned) SPI_OUT);

SPI_IN = SPI_OUT + 1;

}

}

This signal function returns the SPI byte send plus 1 on the next SPI transfer.

SPI_OUT VTREG

Data Type: unsigned int

The SPI_OUT VTREG contains a byte output via the MCU SPI (Serial Peripheral Interface) port. When your simulated program sends a byte via SPI, the SPI_OUT VTREG is set with the value output. You may monitor this VTREG in a simulation script. For example:

signal void spi_watcher (void) {

while (1) {

wwatch (SPI_OUT);

printf ("SPI_OUT: %2.2X\n", (unsigned) SPI_OUT);

}

}

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |