|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Silicon Laboratories, Inc. C8051F120 — Crossbar

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

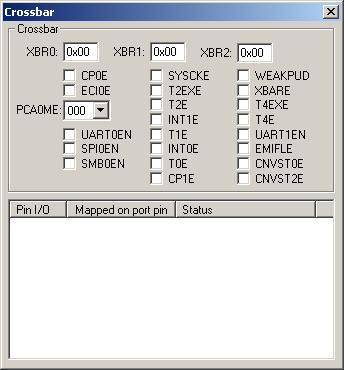

Crossbar Dialog

The Crossbar dialog displays and configures the simulation of the Crossbar peripheral pin assignment capability. The controls in this dialog are separated into three logical groups:

Crossbar Register 0 XBR0 (Port I/O Crossbar Register 0) contains the following control bit settings:

- CPOE (Comparator 0 Output Enable Bit) is set to route CP0 to a port pin.

- ECIOE (PCA0 External Counter Input Enable Bit) is set to route ECIO to a port pin.

- PCA0ME (PCA0 Module I/O Enable Bits) is set to route the CEXn signals to n+1 port pins. n can be 0-4.

- UART0EN (UART0 I/O Enable Bit) is set to route UART0 TX to pin P0.0 and RX to pin P0.1.

- SPIOEN (SPI0 Bus I/O Enable Bit) is set to route SPIO signals MISO, MOSI and NSS to 4 port pins.

- SMB0EN (SMBus0 Bus I/O Enable Bit) is set to route SMBus0 signals SDA and SCL to 2 port pins.

Crossbar Register 1 XBR1 (Port I/O Crossbar Register 1) contains the following control bit settings:

- SYSCKE (SYSCLK Output Enable Bit) is set to route SYSCLK to a port pin.

- T2EXE (T2EX Input Enable Bit) is set to route T2EX to a port pin.

- INT1E (T2 Input Enable Bit) is set to route INT1 to a port pin.

- T1E (T1 Input Enable Bit) is set to route T1 to a port pin.

- INT0E (INT0 Input Enable Bit) is set to route INT0 to a port pin.

- T0E (T0 Input Enable Bit) is set to route T0 to a port pin.

- CP1E (CP1 Output Enable Bit) is set to route CP1 to a port pin.

Crossbar Register 2 XBR2 (Port I/O Crossbar Register 2) contains the following control bit settings:

- WEAKPUD (Weak Pull-Up Disable Bit) is set to disable weak pull-ups.

- XBARE (Crossbar Enable Bit) is set to enable Crossbar. Reset forces all pins on ports 0, 1, 2 and 3 to input mode.

- T4EXE (T4EX Input Enable Bit) is set to route T4EX to a port pin.

- T4E (T4 Input Enable Bit) is set to route T4 to a port pin.

- UART1EN (UART1 I/O Enable Bit) is set to route UART TX and RX to 2 port pins.

- EMIFLE (External Memory Interface Low-Port Enable Bit) if set and external memory is in multiplexed mode, WR and RD and ALE are skipped by the Crossbar. If non-multiplexed mode, only WR and RD are skipped.

- CNVST0E (ADC0 External Convert Start Input Enable Bit) is set to route CNVSTR to a port pin.

- CNVST2E (External Convert Start 2 Input Enable Bit) is set to allow ADC0 conversions from an external input. /LI>

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |