# **ST10**

## FAMILY PROGRAMMING MANUAL

Release 1

Ref: ST10FPM

| TABLE OF                                                                      | CONTENTS                                                                                                                                            | Page                                                 |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1                                                                             | INTRODUCTION                                                                                                                                        | 3                                                    |

| 2                                                                             | STANDARD INSTRUCTION SET                                                                                                                            | 4                                                    |

| 2.1                                                                           | ADDRESSING MODES                                                                                                                                    | 4                                                    |

| 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6                            | Short adressing modes<br>Long addressing mode<br>DPP override mechanism<br>Indirect addressing modes<br>Constants<br>Branch target addressing modes | 4<br>5<br>6<br>7<br>7                                |

| 2.2                                                                           | INSTRUCTION EXECUTION TIMES                                                                                                                         | 8                                                    |

| 2.2.1<br>2.2.2<br>2.2.3                                                       | Definition of measurement units<br>Minimum state times<br>Additional state times                                                                    | 9<br>10<br>10                                        |

| 2.3                                                                           | INSTRUCTION SET SUMMARY                                                                                                                             | 13                                                   |

| 2.4                                                                           | INSTRUCTION SET ORDERED BY FUNCTIONAL GROUP                                                                                                         | 15                                                   |

| 2.5                                                                           | INSTRUCTION SET ORDERED BY OPCODES                                                                                                                  | 26                                                   |

| 2.6                                                                           | INSTRUCTION CONVENTIONS                                                                                                                             | 34                                                   |

| 2.6.1<br>2.6.2<br>2.6.3<br>2.6.4<br>2.6.5<br>2.6.6<br>2.6.7<br>2.6.8          | Instruction name                                                                                                                                    | 34<br>34<br>35<br>35<br>35<br>36<br>37               |

| 2.7                                                                           | ATOMIC AND EXTENDED INSTRUCTIONS                                                                                                                    | 38                                                   |

| 2.8                                                                           | INSTRUCTION DESCRIPTIONS                                                                                                                            | 39                                                   |

| 3                                                                             | MAC INSTRUCTION SET                                                                                                                                 | 123                                                  |

| 3.1                                                                           | ADDRESSING MODES                                                                                                                                    | 123                                                  |

| 3.2                                                                           | MAC INSTRUCTION EXECUTION TIME                                                                                                                      | 124                                                  |

| 3.3                                                                           | MAC INSTRUCTION SET SUMMARY                                                                                                                         | 124                                                  |

| 3.4                                                                           | MAC INSTRUCTION CONVENTIONS                                                                                                                         | 126                                                  |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.6<br>3.4.7<br>3.4.8 | Operands<br>Operations<br>Abbreviations<br>Data addressing Modes<br>Instruction format<br>Flag states<br>Repeated instruction syntax<br>Shift value | 126<br>126<br>126<br>126<br>127<br>127<br>127<br>127 |

| 3.5                                                                           | MAC INSTRUCTION DESCRIPTIONS                                                                                                                        | 127                                                  |

| 4                                                                             | REVISION HISTORY                                                                                                                                    | 170                                                  |

| <b>A7/</b>                                                                    |                                                                                                                                                     | 1/172                                                |

#### **1 - INTRODUCTION**

This programming manual details the instruction set for the ST10 family of products. The manual is arranged in two sections. Section 1 details the standard instruction set and includes all of the basic instructions.

Section 2 details the extension to the instruction set provided by the MAC. The MAC instructions are only available to devices containing the MAC, refer to the datasheet for device-specific information.

In the standard instruction set, addressing modes, instruction execution times, minimum state times and the causes of additional state times are defined. Cross reference tables of instruction mnemonics, hexadecimal opcode, address modes and number of bytes, are provided for the optimization of instruction sequences.

Instruction set tables ordered by functional group, can be used to identify the best instruction for a given application. Instruction set tables ordered by hexadecimal opcode can be used to identify specific instructions when reading executable code i.e. during the de-bugging phase. Finally, each instruction is described individually on a page of standard format, using the conventions defined in this manual. For ease of use, the instructions are listed alphabetically.

The MAC instruction set is divided into its 5 functional groups: Multiply and Multiply-Accumulate, 32-Bit Arithmetic, Shift, Compare and Transfer Instructions. Two new addressing modes supply the MAC with up to 2 new operands per instruction.

Cross reference tables of MAC instruction mnemonics by address mode, and MAC instruction mnemonic by functional code can be used for quick reference.

As for the standard instruction set, each instruction has been described individually in a standard format according to defined conventions. For convenience, the instructions are described in alphabetical order.

#### 2 - STANDARD INSTRUCTION SET

#### 2.1 - Addressing Modes

#### 2.1.1 - Short adressing modes

The ST10 family of devices use several powerful addressing modes for access to word, byte and bit data. This section describes short, long and indirect address modes, constants and branch target addressing modes. Short addressing modes use an implicit base offset address to specify the 24-bit physical address. Short addressing modes give access to the GPR, SFR or bit-addressable memory spacePhysicalAddress = BaseAddress +  $\Delta$  x ShortAddress.

Note:  $\Delta = 1$  for byte GPRs,  $\Delta = 2$  for word GPRs (see Table 1).

#### Rw, Rb

Specifies direct access to any GPR in the currently active context (register bank). Both 'Rw' and 'Rb' require four bits in the instruction format. The base address of the current register bank is determined by the content of register CP. 'Rw' specifies a 4-bit word GPR address relative to the base address (CP), while 'Rb' specifies a 4 bit byte GPR address relative to the base address (CP).

#### reg

Specifies direct access to any (E)SFR or GPR in the currently active context (register bank). 'reg' requires eight bits in the instruction format. Short 'reg' addresses from 00h to EFh always specify (E)SFRs. In this case, the factor ' $\Delta$ ' equals 2 and the base address is 00'F000h for the standard SFR area, or 00'FE00h for the extended ESFR area. 'reg' accesses to the ESFR area require a preceding EXT\*R instruction to switch the base address. Depending on the opcode of an instruction, either the total word (for word operations), or

Table 1 : Short addressing mode summary

the low byte (for byte operations) of an SFR can be addressed via 'reg'. Note that the high byte of an SFR cannot be accessed by the 'reg' addressing mode. Short 'reg' addresses from F0h to FFh always specify GPRs. In this case, only the lower four bits of 'reg' are significant for physical address generation, therefore it can be regarded as identical to the address generation described for the 'Rb' and 'Rw' addressing modes.

#### bitoff

Specifies direct access to any word in the bit-addressable memory space. bitoff' requires eight bits in the instruction format. Depending on the specified 'bitoff' range, different base addresses are used to generate physical addresses: Short 'bitoff' addresses from 00h to 7Fh use 00'FD00h as a base address, therefore they specify the 128 highest internal RAM word locations (00'FD00h to 00'FDFEh).Short 'bitoff' addresses from 80h to EFh use 00'FF00h as a base address to specify the highest internal SFR word locations (00'FF00h to 00'FFDEh) or use 00'F100h as a base address to specify the highest internal ESFR word locations (00'F100h to 00'F1DEh). 'bitoff' accesses to the ESFR area require a preceding EXT\*R instruction to switch the base address. For short 'bitoff' addresses from F0h to FFh, only the lowest four bits and the contents of the CP register are used to generate the physical address of the selected word GPR.

#### bitaddr

Any bit address is specified by a word address within the bit-addressable memory space (see 'bitoff'), and by a bit position ('bitpos') within that word. Thus, 'bitaddr' requires twelve bits in the instruction format.

| Mnemo   | Phys                                                 | ical Address                                         | Short /                    | Address Range                                |                               | Scope of Access                                                                       |

|---------|------------------------------------------------------|------------------------------------------------------|----------------------------|----------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Rw      | (CP)                                                 | + 2*Rw                                               | Rw                         | = 015                                        | GPRs                          | (Word) 16 values                                                                      |

| Rb      | (CP)                                                 | + 1*Rb                                               | Rb                         | = 015                                        | GPRs                          | (Byte) 16 values                                                                      |

| reg     | 00'FE00h<br>00'F000h<br>(CP)<br>(CP)                 | + 2*reg<br>+ 2*reg<br>+ 2*(reg^0Fh)<br>+ 1*(reg^0Fh) | reg<br>reg<br>reg<br>reg   | = 00hEFh<br>= 00hEFh<br>= F0hFFh<br>= F0hFFh | SFRs<br>ESFRs<br>GPRs<br>GPRs | (Word, Low byte)<br>(Word, Low byte)<br>(Word) 16 values<br>(Bytes) 16 values         |

| bitoff  | 00'FD00h<br>00'FF00h<br>(CP)                         | + 2*bitoff<br>+ 2*(bitoff^FFh)<br>+ 2*(bitoff^0Fh)   | bitoff<br>bitoff<br>bitoff | = 00h7Fh<br>= 80hEFh<br>= F0hFFh             | RAM<br>SFR<br>GPR             | Bit word offset 128 values<br>Bit word offset 128 values<br>Bit word offset 16 values |

| bitaddr | Word offset as with bitoff<br>Immediate bit position |                                                      | bitoff<br>bitpos           | = 00hFFh<br>= 015                            | Any single                    | e bit                                                                                 |

#### 2.1.2 - Long addressing mode

Long addressing mode uses one of the four DPP registers to specify a physical 18-bit or 24-bit address. Any word or byte data within the entire address space can be accessed in this mode. All devices support an override mechanism for the DPP addressing scheme (see section 2.1.3 - DPP override mechanism).

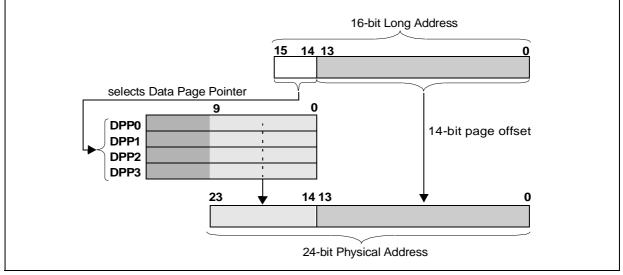

Long addresses (16-bit) are treated in two parts. Bits 13...0 specify a 14-bit data page offset, and bits 15...14 specify the Data Page Pointer (1 of 4). The DPP is used to generate the physical 24-bit address (see Figure 1).

| Figure 1 | : Interpretation of a | 16-bit long address |

|----------|-----------------------|---------------------|

|----------|-----------------------|---------------------|

All ST10 devices support an address space of up to 16MByte, so only the lower ten bits of the selected DPP register content are concatenated with the 14-bit data page offset to build the physical address.

Note: Word accesses on odd byte addresses are not executed, but rather trigger a hardware trap. After reset, the DPP registers are initialized so that all long addresses are directly mapped onto the identical physical addresses, within segment 0.

The long addressing mode is referred to by the mnemonic "mem".

Table 2 : Summary of long address modes

| Mnemo |        | Physical Address | Long Address Range  | Scope of Access  |

|-------|--------|------------------|---------------------|------------------|

| mem   | (DPP0) | mem^3FFFh        | 0000h3FFFh          | Any Word or Byte |

|       | (DPP1) | mem^3FFFh        | 4000h7FFFh          |                  |

|       | (DPP2) | mem^3FFFh        | 8000hBFFFh          |                  |

|       | (DPP3) | mem^3FFFh        | C000hFFFFh          |                  |

| mem   | pag    | mem^3FFFh        | 0000hFFFFh (14-bit) | Any Word or Byte |

| mem   | seg    | mem              | 0000hFFFFh (16-bit) | Any Word or Byte |

#### 2.1.3 - DPP override mechanism

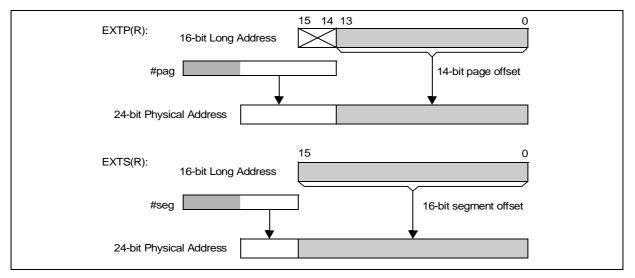

The DPP override mechanism temporarily bypasses the DPP addressing scheme. The EXTP(R) and EXTS(R) instructions override this addressing mechanism. Instruction EXTP(R) replaces the content of the respective DPP register, while instruction EXTS(R) concatenates the complete 16-bit long address with the specified segment base address. The overriding page or segment may be specified directly as a constant (#pag, #seg) or by a word GPR (Rw) (see Figure 2).

#### 2.1.4 - Indirect addressing modes

Indirect addressing modes can be considered as a combination of short and long addressing modes. In this mode, long 16-bit addresses are specified indirectly by the contents of a word GPR, which is specified directly by a short 4-bit address ('Rw'=0 to 15). Some indirect addressing modes add a constant value to the GPR contents before the long 16-bit address is calculated. Other indirect addressing modes allow decrementing or incrementing of the indirect address pointers (GPR content) by 2 or 1 (referring to words or bytes).

In each case, one of the four DPP registers is used to specify the physical 18-bit or 24-bit addresses. Any word or byte data within the entire memory space can be addressed indirectly. Note that EXTP(R) and EXTS(R) instructions override the DPP mechanism.

Instructions using the lowest four word GPRs (R3...R0) as indirect address pointers are specified by short 2-bit addresses.

way that all indirect long addresses are directly mapped onto the identical physical addresses.

Physical addresses are generated from indirect address pointers by the following algorithm:

1. Calculate the physical address of the word GPR which is used as indirect address pointer, by using the specified short address ('Rw') and the current register bank base address (CP).

Word accesses on odd byte addresses are not executed, but rather trigger a hardware trap.

After reset, the DPP registers are initialized in a

GPRAddress = (CP) + 2 x ShortAddress

2. Pre-decremented indirect address pointers ('-Rw') are decremented by a data-type-dependent value ( $\Delta = 1$  for byte operations,  $\Delta = 2$  for word operations), before the long 16-bit address is generated:

$(GPRAddress) = (GPRAddress) - \Delta [optional step!]$ 3. Calculate the long 16-bit (Rw + #data16 if selected) address by adding a constant value (if selected) to the content of the indirect address pointer:

Long Address = (GPR Address) + Constant

4. Calculate the physical 18-bit or 24-bit address using the resulting long address and the corresponding DPP register content (see long 'mem' addressing modes).

Physical Address = (DPPi) + Long Address^3FFh 5. Post-Incremented indirect address pointers ('Rw+') are incremented by a data-type-dependent value ( $\Delta$  = 1 for byte operations,  $\Delta$  = 2 for word operations):

(GPR Address) = (GPR Address) +  $\Delta$  [optional step!]

Figure 2 : Overriding the DPP mechanism

The following indirect addressing modes are provided:

Table 3 : Table of indirect address modes

| Mnemonic                  | Notes                                                                                                                                        |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| [Rw]                      | Most instructions accept any GPR (R15R0) as indirect address pointer.<br>Some instructions, however, only accept the lower four GPRs (R3R0). |  |

| [Rw+]                     | The specified indirect address pointer<br>is automatically incremented by 2 or 1<br>(for word or byte data operations) after<br>the access.  |  |

| [-Rw]                     | The specified indirect address pointer<br>is automatically decremented by 2 or 1<br>(for word or byte data operations)<br>before the access. |  |

| [Rw+#data <sub>16</sub> ] | A 16-bit constant and the contents of<br>the indirect address pointer are added<br>before the long 16-bit address is calcu-<br>lated.        |  |

#### 2.1.5 - Constants

57

The ST10 Family instruction set supports the use of wordwide or bytewide immediate constants.

For optimum utilization of the available code storage, these constants are represented in the instruction formats by either 3, 4, 8 or 16 bits.

Therefore, short constants are always zero-extended, while long constants can be trun-

Table 5 : Branch target address summary

cated to match the data format required for the operation:

Table 4 : Table of constants

| Mnemonic            | Word operation                        | Byte operation                       |

|---------------------|---------------------------------------|--------------------------------------|

| #data <sub>3</sub>  | 0000 <sub>h</sub> + data <sub>3</sub> | 00 <sub>h</sub> + data <sub>3</sub>  |

| #data <sub>4</sub>  | 0000 <sub>h</sub> + data <sub>4</sub> | 00 <sub>h</sub> + data <sub>4</sub>  |

| #data <sub>8</sub>  | 0000 <sub>h</sub> + data <sub>8</sub> | data <sub>8</sub>                    |

| #data <sub>16</sub> | data <sub>16</sub>                    | data <sub>16</sub> ^ FF <sub>h</sub> |

| #mask               | 0000 <sub>h</sub> + mask              | mask                                 |

Note: Immediate constants are always signified by a leading number sign "#".

#### 2.1.6 - Branch target addressing modes

Jump and Call instructions use different addressing modes to specify the target address and segment.

Relative, absolute and indirect modes can be used to update the Instruction Pointer register (IP), while the Code Segment Pointer register (CSP) can only be updated with an absolute value.

A special mode is provided to address the interrupt and trap jump vector table situated in the lowest portion of code segment 0.

| Mnemonic           |      | Target Address                | Target Segment | Valio             | d Address Range |

|--------------------|------|-------------------------------|----------------|-------------------|-----------------|

| caddr              | (IP) | = caddr                       | -              | caddr             | = 0000hFFFEh    |

| rel                | (IP) | = (IP) + 2*rel                | -              | rel               | = 00h7Fh        |

|                    | (IP) | = (IP) + 2*(~rel+1)           | -              | rel               | = 80hFFh        |

| [Rw]               | (IP) | $= ((CP) + 2^*Rw)$            | -              | Rw                | = 015           |

| seg                | -    |                               | (CSP) = seg    | seg               | = 0255          |

| #trap <sub>7</sub> | (IP) | = 0000h + 4*trap <sub>7</sub> | (CSP) = 0000h  | trap <sub>7</sub> | = 00h7Fh        |

#### caddr

Specifies an absolute 16-bit code address within the current segment. Branches MAY NOT be taken to odd code addresses.

Therefore, the least significant bit of 'caddr' must always contain a '0', otherwise a hardware trap would occur.

#### rel

Represents an 8-bit signed word offset address relative to the current Instruction Pointer contents which points to the instruction after the branch instruction.

Depending on the offset address range, either forward ('rel'= 00h to 7Fh) or backward ('rel'= 80h to FFh) branches are possible.

The branch instruction itself is repeatedly executed, when 'rel' = '-1' (FF<sub>h</sub>) for a word-sized branch instruction, or 'rel' = '-2' (FEh) for a double-word-sized branch instruction.

#### [Rw]

The 16-bit branch target instruction address is determined indirectly by the content of a word GPR. In contrast to indirect data addresses, indirectly specified code addresses are NOT calculated by additional pointer registers (e.g. DPP registers).

Branches MAY NOT be taken to odd code addresses. Therefore, to prevent a hardware trap, the least significant bit of the address pointer GPR must always contain a '0.

#### seg

Specifies an absolute code segment number. All devices support 256 different code segments, so only the eight lower bits of the 'seg' operand value are used for updating the CSP register.

#### #trap<sub>7</sub>

Specifies a particular interrupt or trap number for branching to the corresponding interrupt or trap service routine by a jump vector table.

Trap numbers from 00h to 7Fh can be specified, which allows access to any double word code location within the address range 00'0000h...00'01FCh in code segment 0 (i.e. the interrupt jump vector table). For further information on the relation between trap numbers and interrupt or trap sources, refer to the device user manual section on "Interrupt and Trap Functions".

#### 2.2 - Instruction execution times

The instruction execution time depends on where the instruction is fetched from, and where the operands are read from or written to.

The fastest processing mode is to execute a program fetched from the internal ROM. In this case most of the instructions can be processed in just one machine cycle.

All external memory accesses are performed by the on-chip External Bus Controller (EBC) which works in parallel with the CPU.

Instructions from external memory cannot be processed as fast as instructions from the internal ROM, because it is necessary to perform data transfers sequentially via the external interface.

In contrast to internal ROM program execution, the time required to process an external program additionally depends on the length of the instructions and operands, on the selected bus mode, and on the duration of an external memory cycle.

Processing a program from the internal RAM space is not as fast as execution from the internal ROM area, but it is flexible (i.e. for loading temporary programs into the internal RAM via the chip's serial interface, or end-of-line programming via the bootstrap loader).

The following description evaluates the minimum and maximum program execution times. which is sufficient for most requirements. For an exact determination of the instructions' state times, the facilities provided by simulators or emulators should be used.

This section defines measurement units, summarizes the minimum (standard) state times of the 16-bit microcontroller instructions, and describes the exceptions from the standard timing.

<u>ل</u>حک

#### 2.2.1 - Definition of measurement units

The following measurement units are used to define instruction processing times:

- [f<sub>CPU</sub>]: CPU operating frequency (may vary from 1MHz to 80MHz).

- [State]: One state time is specified by one CPU clock period. Therefore, one State is used as the basic time unit, because it represents the shortest period of time which has to be considered for instruction timing evaluations.

1 [State]=

$$1/f_{CPU}[s]$$

; for  $f_{CPU}$  = variable= 50[ns]; for  $f_{CPU}$  = 20MHz

[ACT]: ALE (Address Latch Enable) Cycle Time specifies the time required to perform one external memory access. One ALE Cycle Time consists of either two (for demultiplexed external bus modes) or three (for multiplexed external bus modes) state times plus a number of state times, which is determined by the number of waitstates programmed in the MCTC (Memory Cycle Time Control) and MTTC (Memory Tristate Time Control) bit fields of the SYSCON/BUSCONx registers.

For demultiplexed external bus modes:

1\*ACT =

$$(2 + (15 - MCTC) + (1 - MTTC)) * States$$

= 100 n... 900 ns ; for  $f_{CPU}$  = 20MHz

For multiplexed external bus modes:

1\*ACT = (3 + (15 - MCTC) + (1 - MTTC)) \* States= 150ns ... 950ns ; for  $f_{CPU} = 20MHz$

$T_{tot}$  The total time ( $T_{tot}$ ) taken to process a particular part of a program can be calculated by the sum of the single instruction processing times ( $T_{In}$ ) of the considered instructions plus an offset value of 6 state times which takes into account the solitary filling of the pipeline:

$T_{tot} = T_{11} + T_{12} + ... + T_{1n} + 6 \cdot States$

$T_{ln}$  The time ( $T_{ln}$ ) taken to process a single instruction, consists of a minimum number ( $T_{lmin}$ ) plus an additional number ( $T_{ladd}$ ) of instruction state times and/or ALE Cycle Times:

$T_{In} = T_{Imin} + T_{Iadd}$

#### 2.2.2 - Minimum state times

The table below shows the minimum number of state times required to process an instruction fetched from the internal ROM ( $T_{\text{Imin}}$  (ROM)). This table can also be used to calculate the minimum number of state times for instructions fetched from the internal RAM ( $T_{\text{Imin}}$  (RAM)), or ALE Cycle Times for instructions fetched from the external memory ( $T_{\text{Imin}}$  (ext)).

Most of the 16-bit microcontroller instructions (except some branch, multiplication, division and a special move instructions) require a minimum of two state times. For internal ROM program execution, execution time has no dependence on instruction length, except for some special branch situations.

To evaluate the execution time for the injected target instruction of a cache jump instruction, it can be considered as if it was executed from the internal ROM, regardless of which memory area the rest of the current program is really fetched from.

For some of the branch instructions the table below represents both the standard number of state times (i.e. the corresponding branch is taken) and an additional  $T_{\rm Imin}$  value in parentheses, which refers to the case where, either the branch condition is not met, or a cache jump is taken.

| Instruction                            | <sup>7</sup> Imin<br>(ROM)<br>[States] |     | 7 <sub>lmin</sub> (ROM)<br>(20MHz<br>CPU clk) |       |

|----------------------------------------|----------------------------------------|-----|-----------------------------------------------|-------|

| CALLI, CALLA                           | 4                                      | (2) | 200                                           | (100) |

| CALLS, CALLR, PCALL                    | 4                                      |     | 200                                           |       |

| JB, JBC, JNB, JNBS                     | 4                                      | (2) | 200                                           | (100) |

| JMPS                                   | 4                                      |     | 200                                           |       |

| JMPA, JMPI, JMPR                       | 4                                      | (2) | 200                                           | (100) |

| MUL, MULU                              | 10                                     |     | 500                                           |       |

| DIV, DIVL, DIVU, DIVLU                 | 20                                     |     | 1000                                          |       |

| MOV[B] Rn, [Rm + #data <sub>16</sub> ] | 4                                      |     | 200                                           |       |

| RET, RETI, RETP, RETS                  | 4                                      |     | 200                                           |       |

| TRAP                                   | 4                                      |     | 200                                           |       |

| All other instructions                 | 2                                      |     | 100                                           |       |

Table 6 : Minimum instruction state times [Unit = ns]

Instructions executed from the internal RAM require the same minimum time as they would if

they were fetched from the internal ROM, plus an instruction-length dependent number of state times, as follows:

- For 2-byte instructions:  $T_{Imin}(RAM) = T_{Imin}(ROM) + 4 * States$

- For 4-byte instructions:  $T_{\text{Imin}}(\text{RAM}) = T_{\text{Imin}}(\text{ROM}) + 6 \cdot \text{States}$

Unlike internal ROM program execution, the minimum time  $T_{\text{Imin}}(\text{ext})$  to process an external instruction also depends on instruction length.  $T_{\text{Imin}}(\text{ext})$  is either 1 ALE Cycle Time for most of the 2-byte instructions, or 2 ALE Cycle Times for most of the 4-byte instructions.

The following formula represents the minimum execution time of instructions fetched from an external memory via a 16-bit wide data bus:

- For 2-byte instructions:

T<sub>Imin</sub>(ext) = 1\*ACT + (T<sub>Imin</sub>(ROM) 2) \* States

- For 4-byte instructions: T<sub>Imin</sub>(ext) = 2\*ACTs + (T<sub>Imin</sub>(ROM) - 2) \* States

- Note: For instructions fetched from an external memory via an 8-bit wide data bus, the minimum number of required ALE Cycle Times is twice the number for those of a 16-bit wide bus.

#### 2.2.3 - Additional state times

Some operand accesses can extend the execution time of an instruction  $T_{\text{In}}$ . Since the additional time  $T_{\text{ladd}}$  is generally caused by internal instruction pipelining, it may be possible to minimize the effect by rearranging the instruction sequences. Simulators and emulators offer a high level of programmer support for program optimization.

The following operands require additional state times:

**Internal ROM operand reads:**  $T_{ladd} = 2 * States$ Both byte and word operand reads always require 2 additional state times.

#### Internal RAM operand reads via indirect addressing modes: $T_{ladd} = 0$ or 1 \* State

Reading a GPR or any other directly addressed operand within the internal RAM space does NOT cause additional state time. However, reading an indirectly addressed internal RAM operand will extend the processing time by 1 state time, if the preceding instruction auto-increments or auto-decrements a GPR, as shown in the following example:

In this case, the additional time can be avoided by putting another suitable instruction before the instruction  $I_{n+1}$  indirectly reading the internal RAM.

**Internal SFR operand reads:**  $T_{ladd} = 0, 1 \cdot \text{State or } 2 \cdot \text{States}$ SFR read accesses do NOT usually require additional processing time. In some rare cases, however, either one or two additional state times will be caused by particular SFR operations:

Reading an SFR immediately after an instruction, which writes to the internal SFR space, as shown in the following example:

| In               | : MOV | T0, #1000h | ; write to Timer O                                 |

|------------------|-------|------------|----------------------------------------------------|

| I <sub>n+1</sub> | : ADD | R3, T1     | ; read from Timer 1: T <sub>Iadd</sub> = 1 * State |

Reading the PSW register immediately after an instruction which implicitly updates the flags as shown in the following example:

| In               | : ADD  | R0, #1000h | ; implicit modification of PSW flags                       |

|------------------|--------|------------|------------------------------------------------------------|

| I <sub>n+1</sub> | : BAND | С, Z       | ; read from PSW: T <sub>ladd</sub> = 2 <sub>*</sub> States |

Implicitly incrementing or decrementing the SP register immediately after an instruction which explicitly writes to the SP register, as shown in the following example:

| In               | : MOV SP, #0FB00h | ; explicit update of the stack pointer     |

|------------------|-------------------|--------------------------------------------|

| I <sub>n+1</sub> | : SCXT R1, #1000h | ; implicit decrement of the stack pointer: |

|                  |                   | ; T <sub>Iadd</sub> = 2 * States           |

In each of these above cases, the extra state times can be avoided by putting other suitable instructions before the instruction  $I_{n+1}$  reading the SFR.

#### External operand reads: T<sub>ladd</sub> = 1 \* ACT

Any external operand reading via a 16-bit wide data bus requires one additional ALE Cycle Time. Reading word operands via an 8-bit wide data bus takes twice as much time (2 ALE Cycle Times) as the reading of byte operands.

#### External operand writes: T<sub>ladd</sub> = 0 \* State ... 1 \* ACT

Writing an external operand via a 16-bit wide data bus takes one additional ALE Cycle Time. For timing calculation of the external program parts, this extra time must always be considered. The value of  $T_{ladd}$  which must be considered for timing evaluations of internal program parts, may fluctuate between 0 state times and 1 ALE Cycle Time. This is because external writes are normally performed in parallel to other CPU operations. Thus,  $T_{ladd}$  could already have been considered in the standard processing time of another instruction. Writing a word operand via an 8-bit wide data bus requires twice as much time (2 ALE Cycle Times) as the writing of a byte operand.

Jumps into the internal ROM space:  $T_{ladd} = 0$  or 2 \* States The minimum time of 4 state times for standard jumps into the internal ROM space will be extended by 2 additional state times, if the branch target instruction is a double word instruction at a non-aligned double word location (xxx2h, xxx6h, xxxAh, xxxEh), as shown in the following example:

```

label

; any non-aligned double word instruction

: ....

; (e.g. at location OFFEh)

. . . .

: . . . .

: JMPA cc UC, label

; if a standard branch is taken:

In+1

; T_{Iadd} = 2 * States (T_{In} = 6 * States)

```

A cache jump, which normally requires just 2 state times, will be extended by 2 additional state times, if both the cached jump target instruction and the following instruction are non-aligned double word instructions, as shown in the following example:

| label            | :                   | ; any non-aligned double word instruction       |

|------------------|---------------------|-------------------------------------------------|

|                  |                     | ; (e.g. at location 12FAh)                      |

| I <sub>n+1</sub> | :                   | ; any non-aligned double word instruction       |

|                  |                     | ; (e.g. at location 12FEh)                      |

| In+2             | : JMPR cc_UC, label | ; provided that a cache jump is taken:          |

|                  |                     | ; $T_{Iadd} = 2 * States (T_{In} = 4 * States)$ |

If necessary, these extra state times can be avoided by allocating double word jump target instructions to aligned double word addresses (xxx0h, xxx4h, xxx8h, xxxCh).

#### **Testing Branch Conditions:** T<sub>ladd</sub> = 0 or 1 \* States

NO extra time is usually required for a conditional branch instructions to decide whether a branch condition is met or not. However, an additional state time is required if the preceding instruction writes to the PSW register, as shown in the following example:

| In               | : | BSET | USR0  |       | ; | ; implicit modification of PSW flags                        |   |

|------------------|---|------|-------|-------|---|-------------------------------------------------------------|---|

| I <sub>n+1</sub> | : | JMPR | cc_Z, | label | ; | ; test condition flag in PSW: T <sub>Iadd</sub> = 1 * State | 9 |

In this case, the extra state time can be intercepted by putting another suitable instruction before the conditional branch instruction.

#### 2.3 - Instruction set summary

The following table lists the instruction mnemonic by hex-code with operand.

| Table /     |       | Instru                                                                                     |                       |       |                                      | mo                                                              | nic                   | IJУ  | IIE,                                              | x-U                                  | Jue                         | · VV | iui v                                | she                                                                           | Ian                   | u      |                                       |          |                                       |          |                                     |          |                                                        |          |                                                         |             |                                                        |                                         |          |                                                         |      |                                                        |

|-------------|-------|--------------------------------------------------------------------------------------------|-----------------------|-------|--------------------------------------|-----------------------------------------------------------------|-----------------------|------|---------------------------------------------------|--------------------------------------|-----------------------------|------|--------------------------------------|-------------------------------------------------------------------------------|-----------------------|--------|---------------------------------------|----------|---------------------------------------|----------|-------------------------------------|----------|--------------------------------------------------------|----------|---------------------------------------------------------|-------------|--------------------------------------------------------|-----------------------------------------|----------|---------------------------------------------------------|------|--------------------------------------------------------|

| 0x          | ADD   | е<br>Х                                                                                     | ADDC                  | SUB   | ;                                    | шм                                                              | SUBC                  | CMP  | W.                                                | E                                    | XOR                         | AND  | :                                    | мш                                                                            | OR                    | CMP11  | Rw #d.                                |          | CMPD2                                 | CMPD1    | Rw#d4                               | <b>*</b> | CMPD2                                                  | MOVBZ    | Rw Rw                                                   | Ē           |                                                        | MOVBS                                   | MOV      | ata4                                                    | MOV  | ata <sub>4</sub>                                       |

| x1          | ADDB  | Rw <sub>n</sub> , Rw <sub>m</sub>                                                          | ADDCB                 | SUBB  |                                      | השח, השח                                                        | SUBCB                 | CMPB | RwRw                                              |                                      | XORB                        | ANDB |                                      | דש <sub>ח</sub> , דש <sub>ח</sub>                                             | ORB                   | NEG    | Rw.                                   |          | CPLB                                  | NEGB     | Rw.                                 | -        | CPLB                                                   | I        |                                                         | ATOMIC/EXTR | #data <sub>2</sub>                                     |                                         | MOVB     | Rw <sub>n</sub> , #data₄                                | MOVB | Rw <sub>n</sub> , #data₄                               |

| x2          | ADD   | MEM                                                                                        | ADDC                  | SUB   |                                      | VIEIVI                                                          | SUBC                  | CMP  | MEM                                               |                                      | XOR                         | AND  |                                      | VIEIVI                                                                        | OR                    | CMPI   | Rw. MEM                               |          | CMPD2                                 | CMPD1    | Rw MEM                              |          | CMPD2                                                  | MOVBZ    | REG. MEM                                                |             |                                                        | MOVBS                                   | PCALL    | REG, CADDR                                              | MOV  | MEM                                                    |

| x3          | ADDB  | REG, MEM                                                                                   | ADDCB                 | SUBB  |                                      |                                                                 | SUBCB                 | CMPB | REG MEM                                           | YE G.                                | XORB                        | ANDB |                                      | KEG, MEM                                                                      | ORB                   | CoXXX  | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] | CoXXX    | [IDXI⊗], [Rw <sub>m</sub> ⊗]          | CoXXX    | Rw <sub>n</sub> , Rw <sub>m</sub>   | CoSTORE  | Rw <sub>n</sub> , CoREG                                | CoSTORE  | [Rw <sub>n</sub> ®], CoREG                              | CoMOV       | [IDXI⊗], [Rw <sub>m</sub> ⊗]                           |                                         | I        |                                                         | MOVB | REG, MEM                                               |

| x4          | ADD   | MEM, REG                                                                                   | ADDC                  | SUB   |                                      | MEM, REG                                                        | SUBC                  | I    | MEM REG                                           |                                      | XOR                         | AND  |                                      | MEM, REG                                                                      | NO                    | MOV    | [Rw <sub>n</sub> ], MEM               | MOV      | MEM, [Rw <sub>n</sub> ]               | MOVB     | [Rw <sub>n</sub> ], MEM             | MOVB     | [Rw <sub>m</sub> + #d <sub>16</sub> ], Rw <sub>n</sub> | MOV      | Rw <sub>n</sub> , [Rw <sub>m</sub> + #d <sub>16</sub> ] | NOM         | [Rw <sub>m</sub> + #d <sub>16</sub> ], Rw <sub>n</sub> |                                         | MOVB     | Rw <sub>n</sub> , [Rw <sub>m</sub> + #d <sub>16</sub> ] | MOVB | [Rw <sub>m</sub> + #d <sub>16</sub> ], Rw <sub>n</sub> |

| x5          | ADDB  | ME                                                                                         | ADDCB                 | SUBB  |                                      |                                                                 | SUBCB                 | I    | MF                                                |                                      | XORB                        | ANDB |                                      | M                                                                             | ORB                   |        | I                                     |          | I                                     | DISWDT   |                                     | EINIT    |                                                        | MOVBZ    | MEM. REG.                                               |             |                                                        | MOVBS                                   | I        |                                                         | I    |                                                        |

| x6          | ADD   | data <sub>16</sub>                                                                         | ADDC                  | SUB   | -1                                   | Jala16                                                          | SUBC                  | CMP  | Jata                                              | 91000                                | XOR                         | AND  |                                      | uata <sub>16</sub>                                                            | OR                    | CMP11  | Rw#dae                                |          | CMP12                                 | CMPD1    | Rw#d.e                              | 0        | CMPD2                                                  | SCXT     | REG, #d <sub>16</sub>                                   | SCXT        | REG, MEM                                               |                                         | MOV      | ata# <sub>16</sub>                                      | MOV  | REG                                                    |

| х7          | ADDB  | REG, #data <sub>16</sub>                                                                   | ADDCB                 | SUBB  |                                      | *<br>9<br>4                                                     | SUBCB                 | CMPB | RFG, #data.                                       |                                      | XORB                        | ANDB |                                      | REG, #uala <sub>16</sub>                                                      | ORB                   | IDLE   |                                       | PWRDN    |                                       | SRVWDT   |                                     | SRST     |                                                        | I        |                                                         | EXTP(R)/    | EXTS(R)                                                | #pag, #data2                            | MOVB     | REG, Data# <sub>16</sub>                                | MOVB | MEM, REG                                               |

| x8          | ADD   | [Rw <sub>i</sub> ]<br>Rw <sub>i</sub> +]<br>data                                           | ADDC                  | SUB   | [Rwi]                                | data <sub>3</sub>                                               | SUBC                  | CMP  | [Rw;]<br>Rw:+]                                    | data <sub>3</sub>                    | XOR                         | AND  | [Rwi]                                | ≺w <sub>i</sub> +j<br>data <sub>3</sub>                                       | S                     | MOV    | , Rw <sub>n</sub>                     | MOV      | kw <sub>m</sub> +]                    | MOV      | Rw <sub>m</sub>                     | MOV      | Rwn                                                    | MOV      | [Rw <sub>m</sub> ]                                      | MOV         |                                                        |                                         | MOV      | Rw <sub>m</sub> +]                                      | I    |                                                        |

| 6x          | ADDB  | Rw <sub>n</sub> , [Rw <sub>i</sub> ]<br>Rw <sub>n</sub> , [Rw <sub>i</sub> +]<br>Rw #data_ | ADDCB ADDC            | SUBB  | Rw <sub>n</sub> , [Rw <sub>i</sub> ] | רא <sub>n</sub> , וראיד<br>Rw <sub>n</sub> , #data <sub>3</sub> | SUBCB                 | CMPB | Rw <sub>n</sub> , [Rw <sub>i</sub> ]<br>Rw [Rw.+] | Rw <sub>n</sub> , #data <sub>3</sub> | XORB                        | ANDB | Rw <sub>n</sub> , [Rw <sub>i</sub> ] | кw <sub>n</sub> , [кw <sub>i</sub> +]<br>Rw <sub>n</sub> , #data <sub>3</sub> | ORB                   | MOVB   | [-Rw <sub>m</sub> ], Rw <sub>n</sub>  | MOVB MOV | Rw <sub>n</sub> , [Rw <sub>m</sub> +] | MOVB MOV | [Rw <sub>n</sub> ], Rw <sub>m</sub> | MOVB     | [Rw <sub>m</sub> ], Rw <sub>n</sub>                    | MOVB     | [Rw <sub>n</sub> ], [Rw <sub>m</sub> ]                  | MOVB        |                                                        | [Rw <sub>n+</sub> ], [Rw <sub>m</sub> ] | MOVB     | [Rw <sub>n</sub> ], [Rw <sub>m</sub> +]                 | I    |                                                        |

| хA          | BFLDL | BITOFF, MASK,<br>#data <sub>3</sub>                                                        | BFLDH                 | BCMP  | BITadd, BITadd                       | BMOVN                                                           | BITadd, BITadd        | BMOV | BITadd, BITadd                                    | BOR                                  | BITadd, BITadd              | BAND | BITadd, BITadd                       | BXOR                                                                          | BITadd, BITadd        | JB     | RITadd RFI                            |          | JNB                                   | JBC      | BITadd BITadd                       | 6000 I   | JNBS                                                   | CALLA    | CC, CADDR                                               | CALLS       |                                                        | SEG, CADDDR                             | JMPA     | CC, CADDR                                               | SAML | SEG, CADDR                                             |

| хВ          | MUL   | Rw <sub>n</sub> , Rw <sub>m</sub>                                                          | MULU                  | PRIOR | Rw <sub>n</sub> , Rw <sub>m</sub>    |                                                                 | I                     | DIV  | Rw <sub>n</sub>                                   | DIVU                                 | $Rw_{n}$                    | DIVL | Rwn                                  | DIVLU                                                                         | Rw <sub>n</sub>       | -      |                                       | TRAP     | #trap                                 | CALLI    | cc, [Rw <sub>n</sub> ]              | CALLR    | REL                                                    | RET      |                                                         | RETS        |                                                        |                                         | RETP     | REG                                                     |      | RETI                                                   |

| ×C          | ROL   | RWn, RWm<br>ROL                                                                            | Rw <sub>n</sub> , #d₄ | ROR   | Rw <sub>n</sub> , Rw <sub>m</sub> F  | ROR                                                             | Rw <sub>n</sub> , #d₄ | SHL  | Rw <sub>n</sub> , Rw <sub>m</sub>                 | SHL                                  | ${\sf Rw}_{\sf n}, {\#d}_4$ | SHR  | Rw <sub>n</sub> , Rw <sub>m</sub>    | SHR                                                                           | Rw <sub>n</sub> , #d₄ | I      |                                       | JMPI     | cc, [Rw <sub>n</sub> ]                | ASHR     | Rw <sub>n</sub> , Rw <sub>m</sub>   | ASHR     | Rw <sub>n</sub> , #d <sub>4</sub>                      | NOP      |                                                         | EXTP(R)/    | EXTS(R)                                                | Rw <sub>m</sub> , #d <sub>2</sub>       | PUSH     | REG                                                     | )    | РОР                                                    |

| хD          |       |                                                                                            |                       |       |                                      |                                                                 |                       | •    |                                                   |                                      |                             |      |                                      | JM                                                                            | PR o                  | cc, re | el                                    |          |                                       | -        |                                     | <u>.</u> |                                                        | <u>.</u> |                                                         |             |                                                        |                                         | <u>.</u> |                                                         |      |                                                        |

| Ř           |       |                                                                                            |                       |       |                                      |                                                                 |                       |      |                                                   |                                      |                             |      |                                      | BCLR                                                                          | BIT                   | add    | rQ.q                                  |          |                                       |          |                                     |          |                                                        |          |                                                         |             |                                                        |                                         |          |                                                         |      |                                                        |

| хF          |       |                                                                                            |                       |       |                                      |                                                                 |                       |      |                                                   |                                      |                             |      |                                      | BSET                                                                          | BIT                   | add    | rQ.q                                  |          |                                       |          |                                     |          |                                                        |          |                                                         |             |                                                        |                                         |          |                                                         |      |                                                        |

| High<br>Low | 0×0   | 5                                                                                          | 1x                    |       | 2X                                   | 3х                                                              |                       | ~    | **                                                | 5x                                   | 5                           |      | 6X                                   | 7×                                                                            | 4                     | å      | Xo                                    |          | 9X                                    | , v      | ž                                   | à        | ň                                                      | ζ        | CX                                                      |             | Ď                                                      |                                         | Ĵ        | ĭ                                                       | ΕX   |                                                        |

Table 7 : Instruction mnemonic by hex-code with operand

**A7/**

13/172

Table 8 lists the instructions by their mnemonic and identifies the addressing modes that may be used with a specific instruction and the instruction length, depending on the selected addressing mode (in bytes).

| Mnemonic   | Addressing Modes                                              | Bytes | Mnemonic        | Addressing Modes                                  | Bytes |

|------------|---------------------------------------------------------------|-------|-----------------|---------------------------------------------------|-------|

| ADD[B]     | Rw <sub>n</sub> <sup>1</sup> , Rw <sub>m</sub> <sup>1</sup>   | 2     | CPL[B]          | Rwn <sup>1</sup>                                  | 2     |

| ADDC[B]    | Rw <sub>n</sub> <sup>1</sup> , [Rw <sub>i</sub> ]             | 2     | NEG[B]          |                                                   |       |

| AND[B]     | Rw <sub>n</sub> <sup>1</sup> , [Rw <sub>i</sub> +]            | 2     | DIV             | Rw <sub>n</sub>                                   | 2     |

| OR[B]      | $Rw_{n}^{1}$ , #data <sub>3</sub>                             | 2     | DIVL            |                                                   |       |

| SUB[B]     | reg, #data <sub>16</sub>                                      | 4     | DIVLU           |                                                   |       |

| SUBC[B]    | reg, mem                                                      | 4     | DIVU            |                                                   |       |

| XOR[B]     | mem, reg                                                      | 4     | MUL             | Rw <sub>n</sub> , Rw <sub>m</sub>                 | 2     |

| ASHR       | Rw <sub>n</sub> , Rw <sub>m</sub>                             | 2     | MULU<br>CMPD1/2 | Rw <sub>n</sub> , #data <sub>4</sub>              | 2     |

| ROL / ROR  | $Rw_n$ , #data <sub>4</sub>                                   | 2     | CMPI1/2         | $Rw_n$ , #data <sub>16</sub>                      | 4     |

| SHL / SHR  | ntw <sub>n</sub> , #data <sub>4</sub>                         | 2     | 0000 11/2       | $Rw_n$ , mem                                      | 4     |

| BAND       | bitaddr <sub>Z.z</sub> , bitaddr <sub>Q.q</sub>               | 4     | CMP[B]          | Rw <sub>n</sub> , Rw <sub>m</sub> <sup>1</sup>    | -     |

| BCMP       |                                                               |       |                 | $[Rw_n, [Rw_i]^1$                                 | 2     |

| BMOV       |                                                               |       |                 | $[Rw_n, [Rw_i]]^1$                                | 2     |

| BMOVN      |                                                               |       |                 |                                                   | 2     |

|            |                                                               |       |                 | Rw <sub>n</sub> , #data <sub>3</sub> <sup>1</sup> |       |

| BOR / BXOR |                                                               |       |                 | reg, #data <sub>16</sub>                          | 4     |

| BCLR       | bitaddr <sub>Q.g</sub> ,                                      | 2     | CALLA           | reg, mem<br>cc, caddr                             | 4     |

| BSET       | Q.q,                                                          | _     | JMPA            |                                                   |       |

| BFLDH      | bitoff <sub>Q</sub> , #mask <sub>8</sub> , #data <sub>8</sub> | 4     | CALLI           | cc, [Rw <sub>n</sub> ]                            | 2     |

| BFLDL      |                                                               |       | JMPI            |                                                   |       |

| MOV[B]     | Rw <sub>n</sub> <sup>1</sup> , Rw <sub>m</sub> <sup>1</sup>   | 2     | CALLS           | seg, caddr                                        | 4     |

|            | Rw <sub>n</sub> <sup>1</sup> , #data <sub>4</sub>             | 2     | JMPS            |                                                   |       |

|            | Rw <sub>n</sub> <sup>1</sup> , [Rw <sub>m</sub> ]             | 2     | CALLR           | rel                                               | 2     |

|            | Rw <sub>n</sub> <sup>1</sup> , [Rw <sub>m</sub> +]            | 2     | JMPR            | cc, rel                                           | 2     |

|            | [Rw <sub>m</sub> ], Rw <sub>n</sub> <sup>1</sup>              | 2     | JB              | bitaddr <sub>Q.q</sub> , rel                      | 4     |

|            | [-Rw <sub>m</sub> ], Rw <sub>n</sub> <sup>1</sup>             | 2     | JBC             |                                                   |       |

|            | [Rw <sub>n</sub> ], [Rw <sub>m</sub> ]                        | 2     | JNB             |                                                   |       |

|            | [Rw <sub>n</sub> +], [Rw <sub>m</sub> ]                       | 2     | JNBS            |                                                   |       |

|            | [Rw <sub>n</sub> ], [Rw <sub>m</sub> +]                       | 2     | PCALL           | reg, caddr                                        | 4     |

|            | reg, #data <sub>16</sub>                                      | 4     | POP             | reg                                               | 2     |

|            | $[Rw_{n}, [Rw_{m} + #data_{16}]^{1}$                          | 4     | PUSH            |                                                   |       |

|            | $[Rw_m + #data_{16}], Rw_n^{-1}$                              | 4     | RETP            |                                                   |       |

|            | $[Rw_n], mem$                                                 | 4     | SCXT            | reg, #data <sub>16</sub>                          | 4     |

|            | mem, [Rw <sub>n</sub> ]                                       | 4     |                 | reg, mem                                          | 4     |

|            | reg, mem                                                      | 4     | PRIOR           | Rw <sub>n</sub> , Rw <sub>m</sub>                 | 2     |

|            | mem, reg                                                      | 4     |                 |                                                   |       |

Table 8 : Mnemonic vs address mode & number of bytes

| Mnemonic | Addressing Modes                     | Bytes | Mnemonic  | Addressing Modes                     | Bytes |

|----------|--------------------------------------|-------|-----------|--------------------------------------|-------|

| MOVBS    | Rw <sub>n</sub> , Rb <sub>m</sub>    | 2     | TRAP      | #trap7                               | 2     |

| MOVBZ    | reg, mem                             | 4     | ATOMIC    | #data <sub>2</sub>                   | 2     |

|          | mem, reg                             | 4     | EXTR      |                                      |       |

|          |                                      |       |           |                                      |       |

| EXTS     | Rw <sub>m</sub> , #data <sub>2</sub> | 2     | EXTP      | Rw <sub>m</sub> , #data <sub>2</sub> | 2     |

| EXTSR    | #seg, #data <sub>2</sub>             | 4     | EXTPR     | #pag, #data <sub>2</sub>             | 4     |

| NOP      | -                                    | 2     | SRST/IDLE | -                                    | 4     |

| RET      |                                      |       | PWRDN     |                                      |       |

| RETI     |                                      |       | SRVWDT    |                                      |       |

| RETS     | =                                    |       | DISWDT    |                                      |       |

|          |                                      |       | EINIT     |                                      |       |

**Table 8 :** Mnemonic vs address mode & number of bytes (continued)

Note 1. Byte oriented instructions (suffix 'B') use Rb instead of Rw (not with [Rw<sub>i</sub>]!).

### 2.4 - Instruction set ordered by functional group

The minimum number of state times required for instruction execution are given for the following configurations: internal ROM, internal RAM, external memory with a 16-bit demultiplexed and multiplexed bus or an 8-bit demultiplexed and multiplexed bus. These state time figures do not take into account possible wait states on external busses or possible additional state times induced by operand fetches. The following notes apply to this summary:

#### Data addressing modes

- Rw: Word GPR (R0, R1, ..., R15).

- Rb: Byte GPR (RL0, RH0, ..., RL7, RH7).

- reg: SFR or GPR (in case of a byte operation on an SFR, only the low byte can be accessed via 'reg').

- mem: Direct word or byte memory location.

- [...]: Indirect word or byte memory location. (Any word GPR can be used as indirect address pointer, except for the arithmetic, logical and compare instructions, where only R0 to R3 are allowed).

- bitaddr: Direct bit in the bit-addressable memory area.

- bitoff: Direct word in the bit-addressable memory area.

- #data<sub>x</sub>: Immediate constant (the number of significant bits that can be user-specified is given by the appendix "x").

- #mask<sub>8</sub>:Immediate 8-bit mask used for bit-field modifications.

#### Multiply and divide operations

The MDL and MDH registers are implicit source and/or destination operands of the multiply and divide instructions.

#### Branch target addressing modes

- caddr: Direct 16-bit jump target address (Updates the Instruction Pointer).

- seg: Direct 8-bit segment address (Updates the Code Segment Pointer).

- rel: Signed 8-bit jump target word offset address relative to the Instruction Pointer of the following instruction.

- #trap7: Immediate 7-bit trap or interrupt number.

#### **Extension operations**

The EXT\* instructions override the standard DPP addressing scheme:

- #pag: Immediate 10-bit page address.

- #seg: Immediate 8-bit segment address.

67/

#### **Branch condition codes**

cc: Symbolically specifiable condition codes

| -,    | <b>,</b> - <b>,</b> |        |                                |

|-------|---------------------|--------|--------------------------------|

| cc_UC | Unconditional       | cc_NE  | Not Equal                      |

| cc_Z  | Zero                | cc_ULT | Unsigned Less Than             |

| cc_NZ | Not Zero            | cc_ULE | Unsigned Less Than or Equal    |

| cc_V  | Overflow            | cc_UGE | Unsigned Greater Than or Equal |

| cc_NV | No Overflow         | cc_UGT | Unsigned Greater Than          |

| cc_N  | Negative            | cc_SLE | Signed Less Than or Equal      |

| cc_NN | Not Negative        | cc_SLT | Signed Less Than               |

| cc_C  | Carry               | cc_SGE | Signed Greater Than or Equal   |

| cc_NC | No Carry            | cc_SGT | Signed Greater Than            |

| cc_EQ | Equal               | cc_NET | Not Equal and Not End-of-Table |

|       |                     |        |                                |

### Table 9 : Arithmetic instructions

| Mne  | emonic                   | Description                                                                              | Int.ROM | Int.RAM | 16-bit N-Mux | 16-bit Mux | 8-bit N-Mux | 8-bit Mux | Bytes |

|------|--------------------------|------------------------------------------------------------------------------------------|---------|---------|--------------|------------|-------------|-----------|-------|

| ADD  | Rw, Rw                   | Add direct word GPR to direct GPR                                                        | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADD  | Rw, [Rw]                 | Add indirect word memory to direct GPR                                                   | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADD  | Rw, [Rw+]                | Add indirect word memory to direct GPR and post-<br>increment source pointer by 2        | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADD  | Rw, #data <sub>3</sub>   | Add immediate word data to direct GPR                                                    | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADD  | reg, #data <sub>16</sub> | Add immediate word data to direct register                                               | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADD  | reg, mem                 | Add direct word memory to direct register                                                | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADD  | mem, reg                 | Add direct word register to direct memory                                                | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADDB | Rb, Rb                   | Add direct byte GPR to direct GPR                                                        | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDB | Rb, [Rw]                 | Add indirect byte memory to direct GPR                                                   | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDB | Rb, [Rw+]                | Add indirect byte memory to direct GPR and post-increment source pointer by 1            | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDB | Rb, #data <sub>3</sub>   | Add immediate byte data to direct GPR                                                    | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDB | reg, #data <sub>16</sub> | Add immediate byte data to direct register                                               | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADDB | reg, mem                 | Add direct byte memory to direct register                                                | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADDB | mem, reg                 | Add direct byte register to direct memory                                                | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADDC | Rw, Rw                   | Add direct word GPR to direct GPR with Carry                                             | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDC | Rw, [Rw]                 | Add indirect word memory to direct GPR with Carry                                        | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDC | Rw, [Rw+]                | Add indirect word memory to direct GPR with Carry and post-increment source pointer by 2 | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDC | Rw, #data <sub>3</sub>   | Add immediate word data to direct GPR with Carry                                         | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDC | reg, #data <sub>16</sub> | Add immediate word data to direct register with Carry                                    | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADDC | reg, mem                 | Add direct word memory to direct register with Carry                                     | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| ADDC | mem, reg                 | Add direct word register to direct memory with Carry                                     | 2       | 8       | 4            | 6          | 8           | 12        | 4     |

| Mn    | emonic                   | Description                                                                              | Int.ROM | Int.RAM | 16-bit N-Mux | 16-bit Mux | 8-bit N-Mux | 8-bit Mux | Bytes |

|-------|--------------------------|------------------------------------------------------------------------------------------|---------|---------|--------------|------------|-------------|-----------|-------|

| ADDCB | Rb, Rb                   | Add direct byte GPR to direct GPR with Carry                                             | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDCB | Rb, [Rw]                 | Add indirect byte memory to direct GPR with Carry                                        | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDCB | Rb, [Rw+]                | Add indirect byte memory to direct GPR with Carry and post-increment source pointer by 1 | 2       | 6       | 2            | 3          | 4           | 6         | 2     |

| ADDCB | Rb, #data <sub>3</sub>   | Add immediate byte data to direct GPR with Carry                                         | 2       | 6       | 2            | 3          | 4           | 6         | 2     |