|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) LPC1110 — Timer 1

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

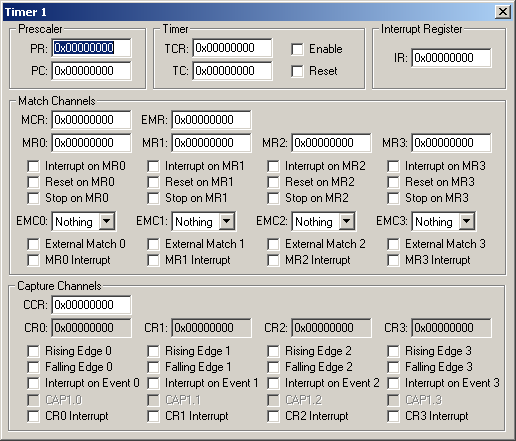

Timer 1 Dialog

The Timer 1 Dialog displays and changes the settings associated with Timer 1. Timers perform various event timing, capture and measurement tasks.

Prescaler Mode

- PR (Prescale Register) contains the number of MCU clocks (PCLK) required to increment the Timer Counter (TC) value.

- PC (Prescale Counter) contains the current prescale counter value. When this value equals the Prescale Register (PR), the Timer (TC) value is incremented.

Timer Control

- TCR (Timer Control Register) contains Timer Enable and Reset control bits.

- TC (Timer Counter) is the timer counter value. It is incremented when the Prescale Counter (PC) equals the Prescale Register (PR).

- Enable is set to enable the Timer.

- Reset is set to reset the Timer.

Interrupt Register

- IR (Interrupt Register) contains the interrupt flags for the seven match channels. When a match channel interrupt is generated, the flag bit in the IR for that match channel is set. Storing a 1 in any of the IR bits resets that match channel interrupt.

Match Channels

- MCR (Match Control Register) controls the Timer reset and interrupt generation when a Match Register (MRx) value equals the Timer Counter (TC) value.

- EMR (External Match Register) enables and configures the behavior of the MAT0/1 output signal.

- MRx (Match Register 0-3) contains a match value that is compared to the Timer Capture value. When they are equal, depending on the Match Control Register (MCR), the MCU may suspend the Timer or Prescaler counting, or generate an interrupt.

- Interrupt on MRx is set to generate an interrupt when the value in MRx matches the Timer Counter (TC) value.

- Reset on MRx is set to reset the Timer Counter value (TC) when the value in MRx matches the Timer Counter (TC) value.

- Stop on MRx is set to stop the Timer Counter value (TC) and the Prescale Counter (PC) when the value in MRx matches the Timer Counter (TC) value.

- EMCx (External Match Control x) defines how the output level is set when an external match occurs on MRx.

- External Match x reflects the state of the output MAT0/1 when a match on MRx occurs.

- MRx Interrupt is set when an MRx matches the value in TC.

Capture Channels

- CCR (Capture Control Register) controls which edge of the capture inputs trigger loading the Capture Registers.

- CRx (Capture Register x) contains the Timer Counter (TC) value when the last capture event occurred for this register.

- Rising Edge x is set to trigger a when a rising edge occurs on the capture event pin (CAP1.x).

- Falling Edge x is set to trigger a when a falling edge occurs on the capture event pin (CAP1.x).

- Interrupt on Event x is set to trigger an interrupt when the capture register (CRx) is loaded.

- CAP1.x (Capture Signals) are signal levels that can be configured to load a Capture Register or generate an interrupt.

- CRx Interrupt is set to trigger a Capture Register (CRx) interrupt.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |