|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Silicon Laboratories, Inc. C8051T600 — PCA Timer with modules

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

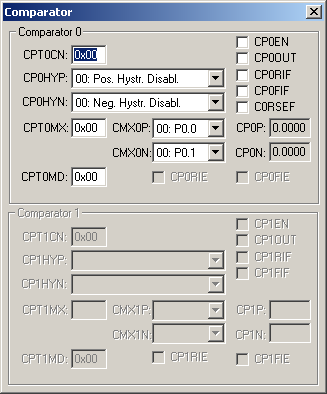

Comparator Dialog

The Comparator Dialog controls simulation of the two voltage comparators in the device. When enabled, it allows the user to compare voltage sources to generate a logic-level signal to a variety of destinations.

Comparator 0

- CPT0CN (Comparator 0 Control Register) contains the following control bit settings:

- CP0EN (Comparator 0 Output Enable Bit) is set to enable comparator 0.

- CP0OUT (Comparator 0 Output State Flag) is set when the voltage on CP0P is greater than CP0N.

- CP0RIF (Comparator 0 Rising-Edge Interrupt Flag) is set when a Comparator 0 rising edge interrupt occurs.

- CP0FIF (Comparator 0 Falling-Edge Interrupt Flag) is set when a Comparator 0 falling edge interrupt occurs.

- CORSEF (Comparator 0 Reset Flag) is set to reset Comparator 0.

- CP0HYP (Comparator 0 Positive Hysteresis Control Bits) selects 0, 2, 4 or 10 mV of positive hysteresis.

- CP0HYN (Comparator 0 Negative Hysteresis Control Bits) selects 0, 2, 4 or 10 mV of negative hysteresis.

- CPT0MX (Comparator 0 MUX Selection Register) contains the positive and negative input controls for CMX0P and CMX0N.

- CMX0P (Comparator 0 Positive Input MUX Select) selects the port pins to be used for positive input.

- CMX0N (Comparator 0 Negative Input MUX Select) selects the port pins to be used for negative input.

- CP0P (Comparator 0 Positive Input Voltage) displays the Comparator 0 negative input voltage.

- CP0N (Comparator 0 Negative Input Voltage) displays the Comparator 0 positive input voltage.

- CPT0MD (Comparator 0 Mode Selection Register) selects the Comparator 0 response time.

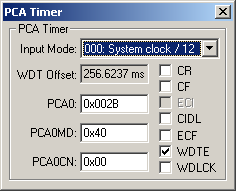

PCA Timer Dialog

The PCA Timer Dialog controls simulation all of the 16-bit PCA counter/timer.

PCA Timer

- Input Mode is the mode for the selected capture/compare register.

- WDT Offset (Watchdog Timer Offset) is the time, in milliseconds, before the WDT will expire.

- PCA0 (PCA Counter Timer Register) holds the counter or timer value used by the PCA.

- PCA0CN (PCA Control Register) contains the PCA Timer run control and overflow flag.

- CR (PCA Counter/Timer Run Control) is set to enable the PCA counter/timer.

- CF (PCA Counter/Timer Overflow Flag) is set to cause a PCA interrupt when an overflow occurs.

- ECI (External Clock Input) is set to use the external clock as the PCA clock source.

- PCA0MD (PCA Mode Register) contains the following control bits:

- CIDL (PCA Counter/Timer Idle Control) is set to suspend PCA operation when the system controller is in idle mode.

- ECF (PCA Counter/Timer Overflow Interrupt Enable) is set to enable a PCA interrupt when CF is set.

- WDTE (Watchdog Timer Enable) is set to enable PCA module 4 as a WDT.

- WDLCK (Watchdog Timer Lock) is set to lock the WDT.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |