|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For NXP (founded by Philips) P89LPC931 — I²C Interface

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

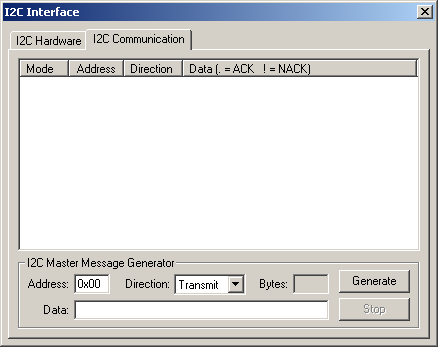

I²C Interface Communication Dialog

The I²C Communication Dialog allows you to view the data sent or received on the I²C bus.

I²C Message Generator Group

- Address contains address of the sending or receiving device.

- Direction selects the direction of the message to be sent or received.

- Bytes is the length of the last message in bytes.

- Data is the message data sent or received.

- Generate starts message transmission.

- Stop suspends I²C bus communication.

To clear the message display, double-click anywhere in the message display area.

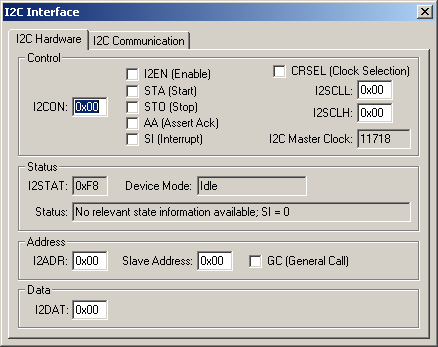

I²C Interface Hardware Dialog

The I²C Hardware Interface dialog displays all configuration options for the on-chip I²C controller. You may interactively alter and view these options using the dialog controls. Simulation of this interface is controlled by the following groups:

Control Group

- I2CON (I²C Control Register) contains the following bits that control the functions of the I²C:

- I2EN (I²C Enable) is set when the I²C is enabled.

- STA (I²C Start Flag) is set when the I²C has started a transmission as a master.

- STO (I²C Stop Flag) is set to send a stop condition on the I²C bus.

- AA (I²C Assert Acknowledge Flag) is set to request that an acknowledge be returned during the acknowledge cycle.

- SI (I²C Serial Interrupt Flag) is set to trigger a I²C interrupt.

Clock Group

- CRSEL (I²C Clock Selection Register) when set, a Timer 1 overflow generates the serial clock (SCL). If reset, the internal SCL generator is used based on the values of I2SCLH and I2SCLL.

- I2SCLH (I²C Serial Clock High) contains the maximum number of PCLK cycles for the internal SCL generator. CRSEL must be reset.

- I2SCLL (I²C Serial Clock Low) contains the minimum number of PCLK cycles for the internal SCL generator. CRSEL must be reset.

- I2C Master Clock is the master clock calculated from the system clock and the SMB0CR value.

Status Group

- I2STAT (I²C Status Register) contains the 8-bit status code.

- Device Mode displays the state of the I²C controller.

- Status a text description of the status code.

Address Group

- I2ADR (I²C Address Register) contains the following values:

- Slave Address (I²C Address Register) contains the slave address of the I²C interface.

- GC (General Call) is set when the general call address is recognized.

Data Group

- I2DAT (I²C Data Register) contains the either the data to be transmitted or the data just received.

I2C_CLK VTREG

Data Type: unsigned long

The I2C_CLK VTREG specifies the clock frequency (in Hz) to use in SLAVE mode. For example:

I2C_CLK = 100000

specifies a clock frequency of 100KHz.

I2C_IN VTREG

Data Type: unsigned int

The I2C_IN VTREG contains data sent from an I²C peripheral to the simulated MCU. The following values may be written to this register:

- 0x0000-0x00FF: An address or data byte transfer.

- 0x0100: START byte. This initiates a SLAVE transmit or receive. The next byte sent is the address.

- 0xFF00: ACK.

- 0xFF01: NACK.

- 0xFFFF: IDLE or STOP condition.

I2C_OUT VTREG

Data Type: unsigned int

The I2C_OUT VTREG contains data sent from the simulated MCU to the I²C peripheral. The following values are possible:

- 0x0000-0x00FF: An address or data byte transfer.

- 0x0100: START byte. This initiates a MASTER transmit or receive. The next byte sent is the address.

- 0xFF00: ACK.

- 0xFF01: NACK.

- 0xFFFF: IDLE or STOP condition.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |