|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Atmel AT91R40807 — Timer Counter Block (3 Channels)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

These simulation capabilities are described below.

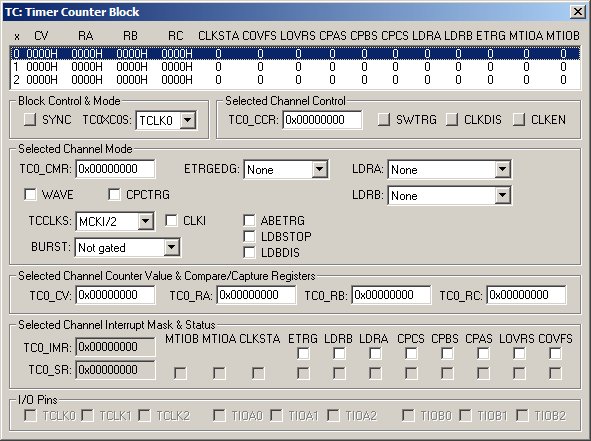

Timer Counter Block Dialog

The Timer/Counter Block Dialog displays and changes the settings associated with a Timer/Counter Block. Timer/counters perform various event counting and measurement tasks.

Block & Control Mode

- SYNC creates a synchronization input signal.

- TC0XC0S defines the external clock input signal for this Timer/Counter.

Selected Channel Control

- TC0_CCR displays the Timer/Counter Channel Control Register.

- SWTRG performs a software trigger.

- CLKDIS disables the clock.

- CLKEN enables the clock.

Selected Channel Mode

- TC0CMR displays the Timer/Counter Capture Mode Register.

- WAVE enables Waveform mode.

- CPCTRG resets the counter and starts the clock.

- TCCLKS selects the source and time base of the clock signal.

- CKLI (Clock Invert) increments the falling edge of the clock.

- BURST gates the clock by a selected external signal.

- ABETRG (TIOA/TIOB External Trigger) uses TIOA as an external trigger when checked. Uses TIOB when not checked.

- LDBSTOP stops the counter clock when RB loading occurs.

- LDBDIS disables the counter clock when RB loading occurs.

- ETRGEDG selects the rising edge, falling edge or both for an external trigger.

- LDRA selects loading of register A on the rising edge of TIOA, falling edge or both.

- LDRB selects loading of register B on the rising edge of TIOA, falling edge or both.

Selected Channel Counter Value & Compare/Capture Registers

- TC0_CV holds the Timer/Counter value.

- TC0_RA holds the Timer/Counter Register A value.

- TC0_RB holds the Timer/Counter Register B value.

- TC0_RC holds the Timer/Counter Register C value.

Selected Channel Interrupt Mask & Status

- TC0_IMR displays the Timer/Counter Interrupt Mask Register.

- TC0_SR displays the Timer/Counter Status Register.

- MTIOB (TIOB Mirror) if set, TIOB is high and if WAVE is set, TIOB is driven high.

- MTIOA (TIOA Mirror) if set, TIOA is high and if WAVE is set, TIOA is driven high.

- CLKSTA (Clock Status) if set, clock is enabled.

- ETRG is set if an external trigger occurred after reading the Status Register.

- LDRB is set if register B loading occurred after reading the Status Register.

- LDRA is set if register A loading occurred after reading the Status Register.

- CPCS is set if register C compare occurred after reading the Status Register.

- CPBS is set if register B compare occurred after reading the Status Register.

- CPAS is set if register A compare occurred after reading the Status Register.

- LOVRS is set if registers A or B were loaded 2 or more times but not read after reading the Status Register.

- COVFS is set if a counter overflowed after reading the Status Register.

I/O Pins

- TCLK0 is the Timer 0 Clock signal input.

- TCLK1 is the Timer 1 Clock signal input.

- TCLK2 is the Timer 2 Clock signal input.

- TIOA0 is the Timer 0 Signal A input.

- TIOA1 is the Timer 1 Signal A input.

- TIOA2 is the Timer 2 Signal A input.

- TIOB0 is the Timer 0 Signal B input.

- TIOB1 is the Timer 1 Signal B input.

- TIOB2 is the Timer 2 Signal B input.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |