|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For Atmel AT91M40800 — Parallel I/O Controller (32 I/O Lines)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

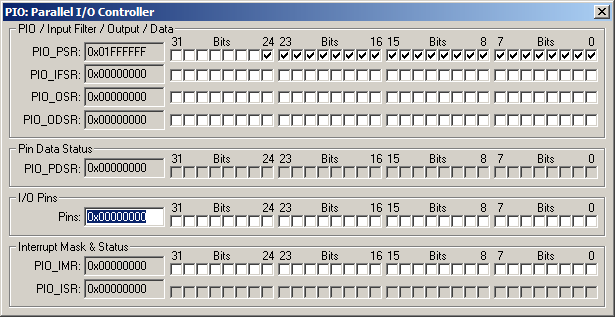

Parallel I/O Controller Dialog

The PIO Dialog box allows you to configure the parallel I/O port using checkboxes. Controls in this dialog are presented in the following groups.

PIO/Input Filter/Output/Data Group

- The PIO_PSR check boxes indicate which pins are controlled by the associated peripheral (0-unchecked) and which pins are controlled by the PIO (1-checked). Changing the values of these check boxes changed the values of the PIO_PER and PIO_PDR peripheral registers.

- The PIO_IFSR check boxes indicate that glitch filtering is enabled (1-checked) for the corresponding pin. Changing these check boxes writes to the PIO_IFER or PIO_IFDR peripheral registers.

- The PIO_OSR check boxes indicate the output status (0-unchecked for input, 1-checked for output) of the corresponding pin. Changing these check boxes writes to the PIO_OER or PIO_ODR peripheral registers.

- The PIO_ODSR check boxes indicate the output value for each port pin. Changing these check boxes writes to the PIO_SODR or PIO_CODR peripheral registers.

Pin Data Status Group

- The PIO_PDSR check boxes indicate the pin data status of the pins on the simulated MCU.

I/O Pins Group

- The Pins check boxes indicate the states of the pins on the simulated MCU. When used as outputs, these have the same value as the PIO_ODSR check boxes. When used as inputs you may set the level of the input pin to high (1) or low (0).

Interrupt Mask & Status Group

- The PIO_IMR check boxes indicate the interrupts enabled for each corresponding pin. Changing these check boxes writes to the PIO_IER or PIO_IDR peripheral registers.

- The PIO_ISR check boxes allow you to view the interrupt status registers for the PIOA pins.

PORT VTREG

Data Type: unsigned long

The PORT VTREGs represent the I/O pins of the simulated MCU Port. You may read PORT to determine the state of the output pins. For example, in the command window you may type,

PORT

to obtain the value corresponding to the set pins of the port. You may also change the input values of port pins by changing the value of the VTREG. For example,

PORT=0x000000F0

sets the upper four port pins to a value of 1 and all other port pins to a value of 0. You may use the bitwise operators AND(&), OR(|) and XOR(^) to change individual bits of the PORT VTREGs. For example:

PORT |= 0x00000001; /* Set P0 Pin */ PORT &= ~0x00000200; /* Clr P9 Pin */ PORT ^= 0x00800000; /* Toggle P23 Pin */

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |