|

||

| Products Download Events Support Videos | ||

Product Information

Device Database®

Downloads

Compliance Testing

Distributors

Peripheral Simulation

For STMicroelectronics ST10R165 — Clock Managment (Direct Drive or Prescaler)

Simulation support for this peripheral or feature is comprised of:

- Dialog boxes which display and allow you to change peripheral configuration.

- VTREGs (Virtual Target Registers) which support I/O with the peripheral.

These simulation capabilities are described below.

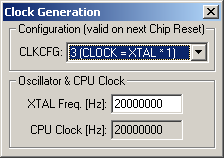

Clock Generation Dialog

The Clock Generation dialog displays and allows you to specify the configuration for the MCU clock.

- CLKCFG specifies the configuration of the clock in relation to the oscillator frequency.

- XTAL Freq. specifies the oscillator frequency in Hz.

CLOCK VTREG

Data Type: unsigned long

The CLOCK VTREG contains the speed of the microcontroller instruction clock (in Hertz). This is effectively the number of 1-cycle instructions that the simulated microcontroller can execute each second. This number is derived by dividing the oscillator frequency (specified by the XTAL VTREG) by a fixed number (12 on standard 8051 devices). The CLOCK VTREG can only be read. It cannot be changed directly. It can only be changed by changing the value of the XTAL VTREG or by changing the clock divisor via the CLKCFG VTREG.

ProductsDevelopment Tools |

Hardware & Collateral |

Downloads |

Support |

Contact |