## PRELIMINARY W79E658A/W79L658A DATA SHEET

### 8-BIT MICROCONTROLLER

### Table of Contents-

| 1.  | GENE  | ERAL DES | SCRIPTION                          | 4  |

|-----|-------|----------|------------------------------------|----|

| 2.  | FEAT  | URES     |                                    | 4  |

| 3.  | PIN C | ONFIGU   | RATION                             | 5  |

| 4.  | PIN D | ESCRIPT  | FION                               | 6  |

|     | 4.1   | Port 4.  |                                    | 7  |

| 5.  | MEM   | ORY ORG  | GANIZATION                         | g  |

|     | 5.1   | Prograr  | m Memory (on-chip Flash)           | g  |

|     | 5.2   | Data M   | emory                              | 10 |

| 6.  | SPEC  | IAL FUN  | CTION REGISTERS                    | 11 |

| 7.  | INST  | RUCTION  | I SET                              | 42 |

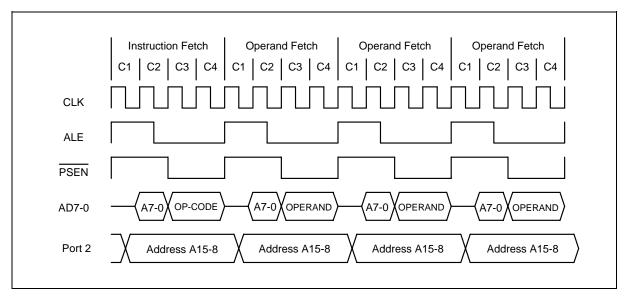

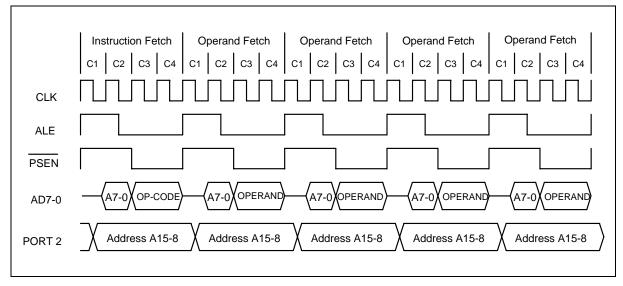

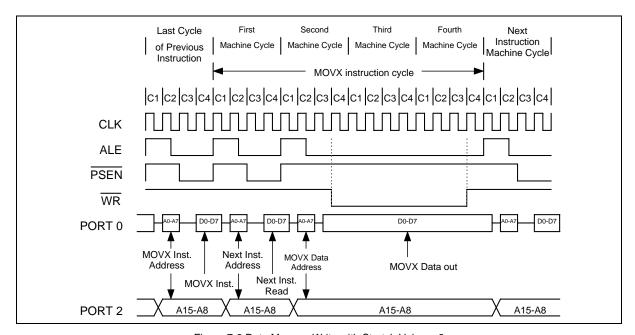

|     | 7.1   |          | ion Timing                         |    |

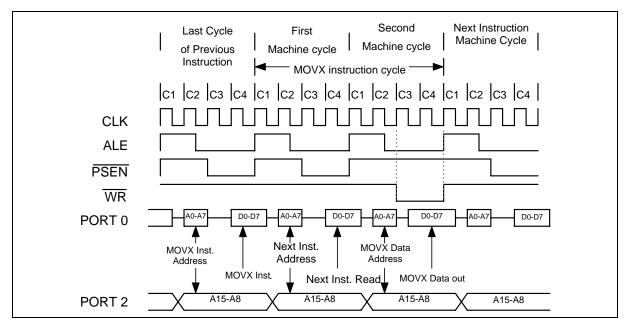

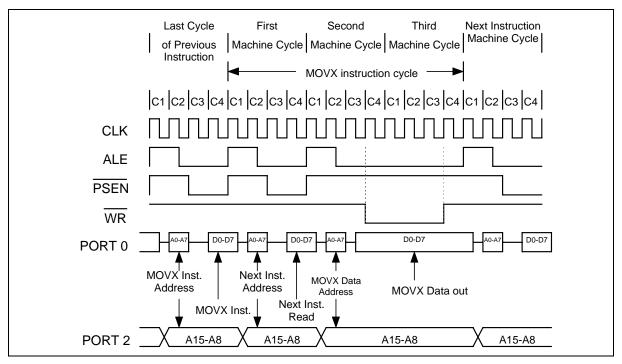

|     |       |          | External Data Memory Access Timing |    |

| 8.  | POW   |          | AGEMENT                            |    |

|     | 8.1   |          | de                                 |    |

|     | 8.2   |          | Down Mode                          |    |

| 9.  | RESE  |          | ITIONS                             |    |

|     | 9.1   |          | Conditions                         |    |

|     | 9.2   |          | l Reset                            |    |

|     | 9.3   |          | On Reset (POR)                     |    |

|     | 9.4   |          | log Timer Reset                    |    |

|     | 9.5   |          | State                              |    |

| 10. |       |          |                                    |    |

|     | 10.1  | •        | ot Sources                         |    |

|     | 10.2  | •        | Level Structure                    |    |

| 11. |       |          | BLE TIMERS/COUNTERS                |    |

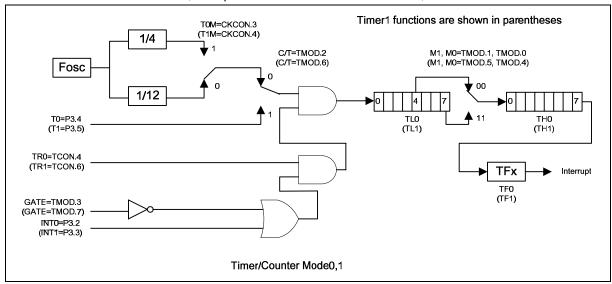

|     | 11.1  |          | Counters 0 & 1                     |    |

|     |       |          | Time-Base Selection                |    |

|     |       |          | Mode 0                             |    |

|     |       |          | Mode 1                             |    |

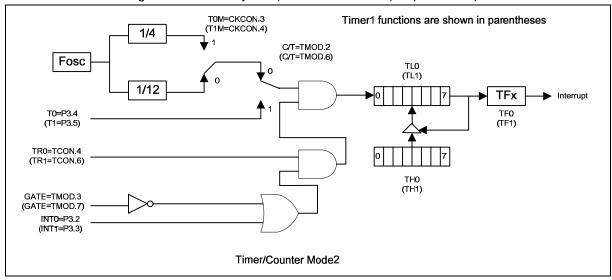

|     |       | 11.1.4   | Mode 2                             |    |

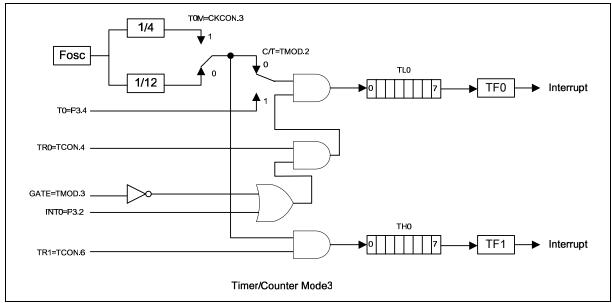

|     |       |          | Mode 3                             |    |

|     | 11.2  |          | Counter 2                          |    |

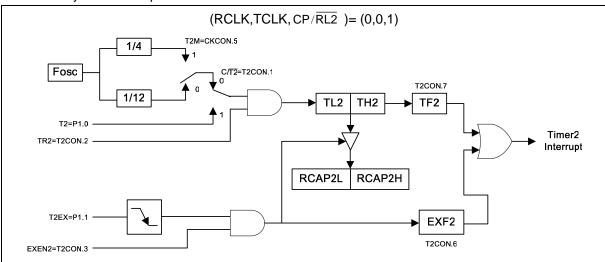

|     |       |          | Capture Mode                       |    |

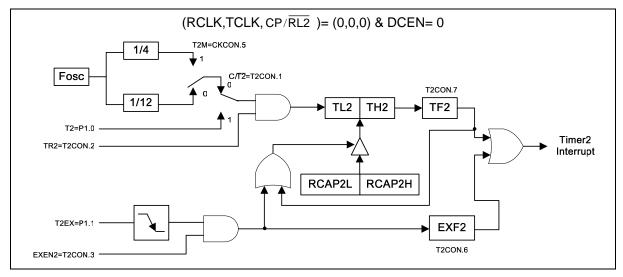

|     |       |          | Auto-reload Mode, Counting up      |    |

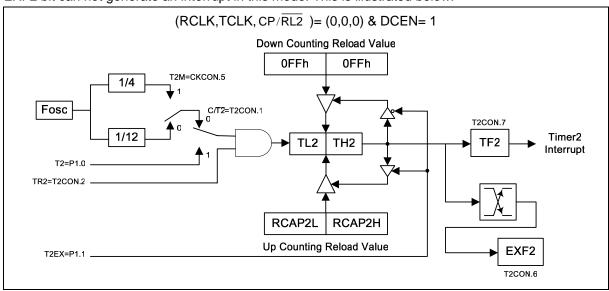

|     |       |          | Auto-reload Mode, Counting Up/Down |    |

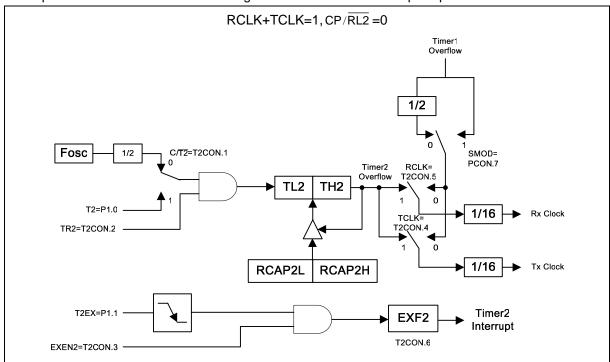

|     |       | 11.2.4   | Baud Rate Generator Mode           | 64 |

- 1 -

# **Esses winbond sesses**

| 12. | WATO  | CHDOG 1  | TIMER                                   | 65  |

|-----|-------|----------|-----------------------------------------|-----|

| 13. | PULS  | E-WIDTH  | H-MODULATED (PWM) OUTPUTS               | 68  |

| 14. | SERI  | AL PORT  | T                                       | 70  |

|     | 14.1  | Mode 0   | O                                       | 70  |

|     | 14.2  | Mode 1   | 1                                       | 71  |

|     | 14.3  | Mode 2   | 2                                       | 72  |

|     | 14.4  | Mode 3   | 3                                       | 74  |

|     | 14.5  | Framin   | g Error Detection                       | 75  |

|     | 14.6  | Multipre | ocessor Communications                  | 75  |

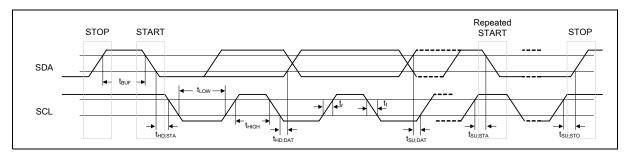

| 15. | I2C S | ERIAL P  | ORTS                                    | 77  |

|     | 15.1  | The I20  | C Control Registers                     | 78  |

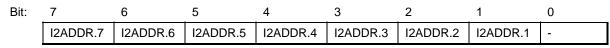

|     |       | 15.1.1   | Slave Address Registers, I2ADDRxx       | 78  |

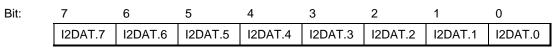

|     |       | 15.1.2   | Data Register, I2DAT                    | 78  |

|     |       | 15.1.3   | Control Register, I2CONx                | 79  |

|     |       | 15.1.4   | Status Register, I2STATUSx              | 79  |

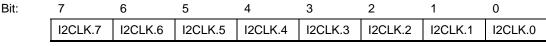

|     |       | 15.1.5   | I2C Clock Baud Rate Control, I2CLKx     | 80  |

|     |       | 15.1.6   | I2C Time-out Counter, I2Timerx          | 80  |

|     | 15.2  | Modes    | of Operation                            | 80  |

|     |       | 15.2.1   | Master Transmitter Mode                 | 80  |

|     |       | 15.2.2   | Master Receiver Mode                    | 81  |

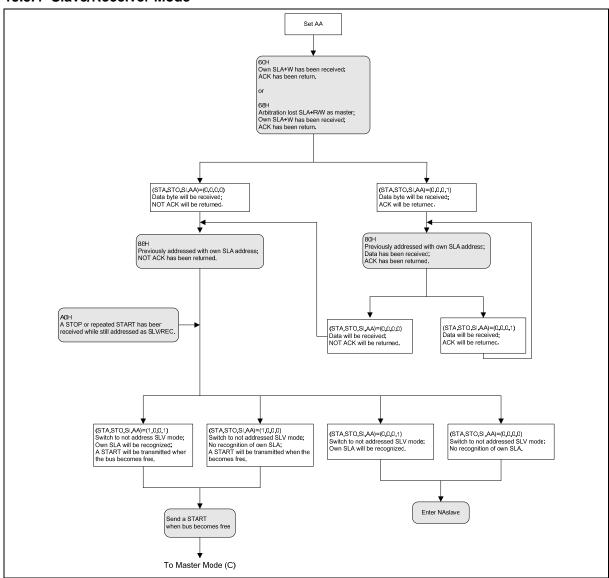

|     |       | 15.2.3   | Slave Receiver Mode                     | 81  |

|     |       | 15.2.4   | Slave Transmitter Mode                  | 81  |

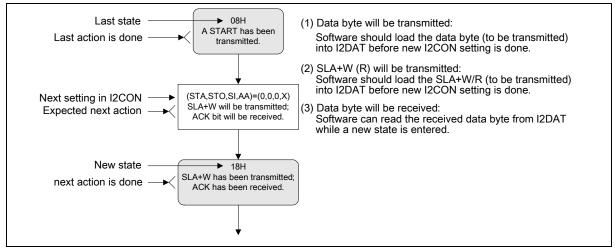

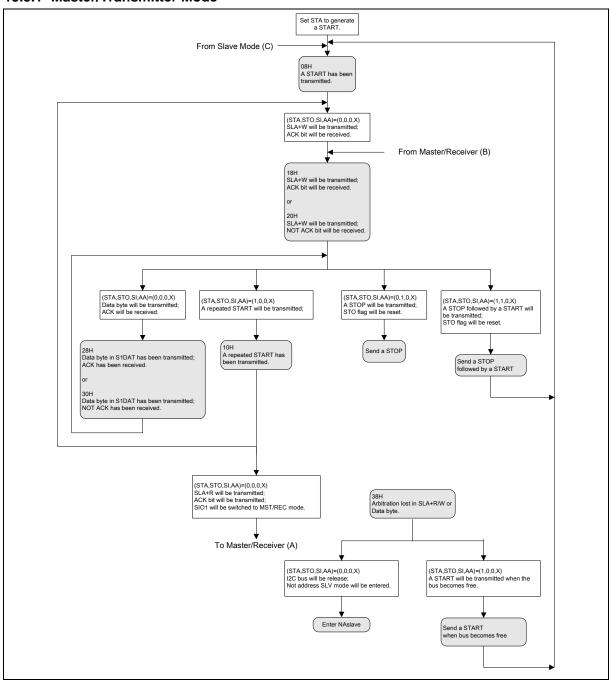

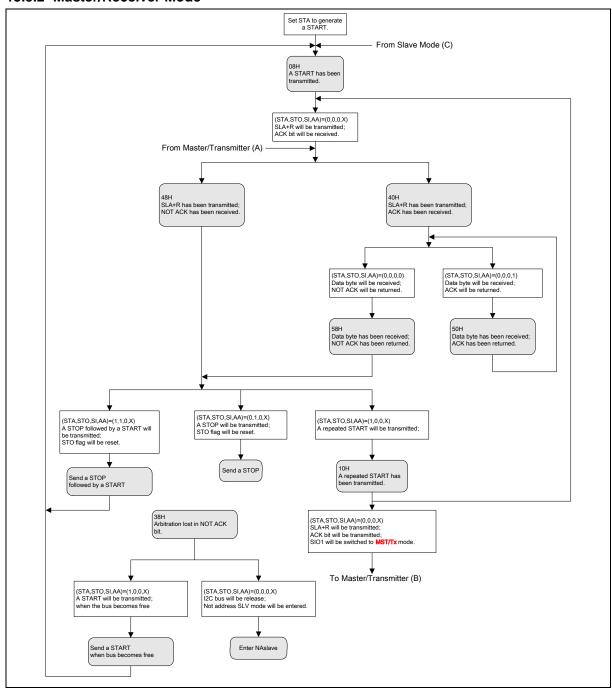

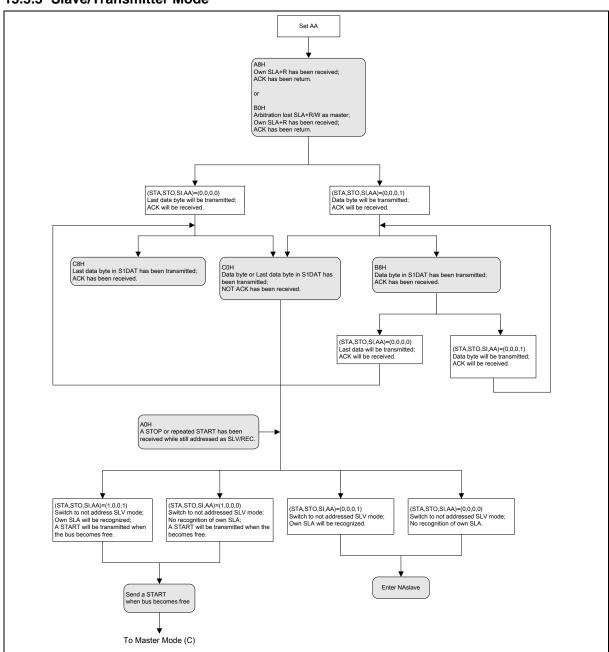

|     | 15.3  | Data T   | ransfer Flow in Four Operating Modes    | 81  |

|     |       | 15.3.1   | Master/Transmitter Mode                 | 82  |

|     |       | 15.3.2   | Master/Receiver Mode                    | 83  |

|     |       | 15.3.3   | Slave/Transmitter Mode                  | 84  |

|     |       | 15.3.4   | Slave/Receiver Mode                     | 85  |

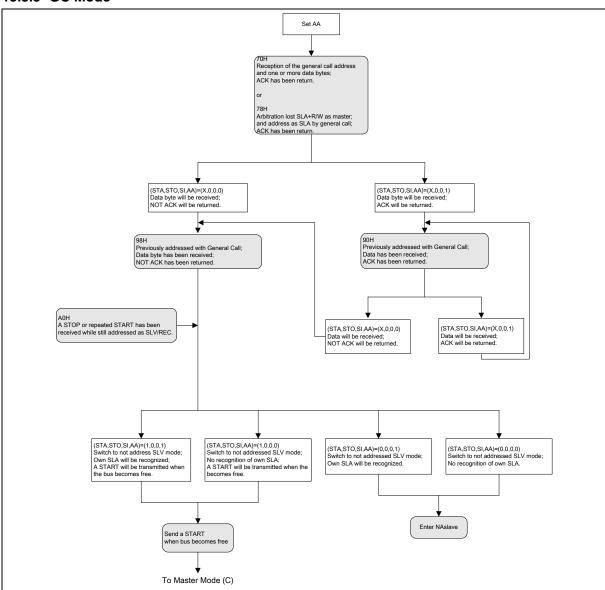

|     |       | 15.3.5   | GC Mode                                 | 86  |

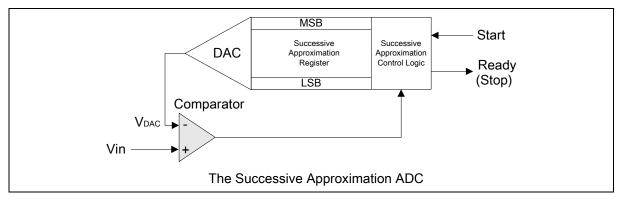

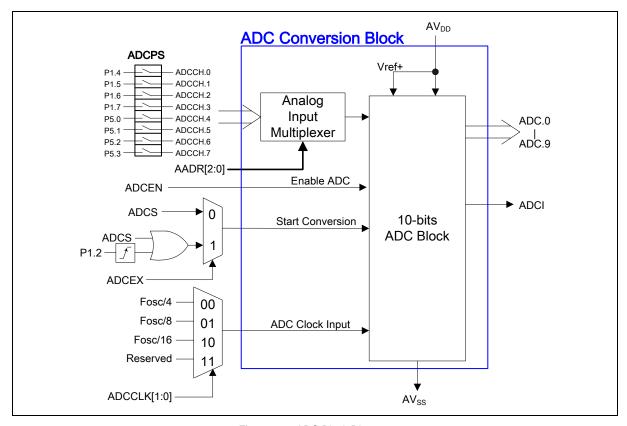

| 16. | ANAL  | .OG-TO-  | DIGITAL CONVERTER                       | 87  |

|     | 16.1  | Operat   | tion of ADC                             | 87  |

|     | 16.2  | ADC R    | Lesolution and Analog Supply            | 88  |

|     | 16.3  | ADC C    | Control Registers                       | 89  |

| 17. | TIME  | D ACCES  | SS PROTECTION                           | 91  |

| 18. | POR1  | Γ4 STRU  | JCTURE                                  | 93  |

| 19. | H/W F | REBOOT   | MODE (BOOT FROM 4K BYTES OF LDFLASH)    | 96  |

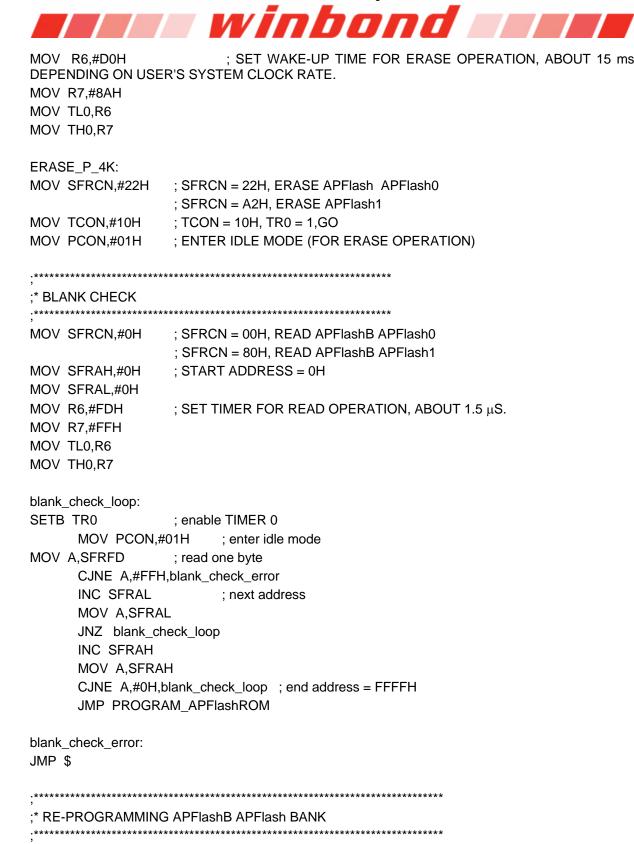

| 20. | IN-SY | STEM P   | ROGRAMMING                              | 97  |

|     | 20.1  | The Lo   | pader Program Locates at LDFlash Memory | 97  |

|     | 20.2  | The Lo   | pader Program Locates at APFlash Memory | 97  |

| 21. | H/W \ | WRITER   | MODE                                    | 97  |

| 22. | SECL  | JRITY BI | TS                                      | 98  |

| 23. | ELEC  | TRICAL   | CHARACTERISTICS                         | 100 |

|     | 23.1  | Absolu   | te Maximum Ratings                      | 100 |

# **Esses winbond sesses**

|     | 23.2  | DC Characteristics                                     | 100 |

|-----|-------|--------------------------------------------------------|-----|

|     | 23.3  | AC Characteristics                                     | 102 |

|     |       | 23.3.1 External Clock Characteristics                  | 102 |

|     |       | 23.3.2 AC Specification                                | 102 |

|     |       | 23.3.3 MOVX Characteristics Using Stretch Memory Cycle | 103 |

|     | 23.4  | The ADC Converter DC ELECTRICAL CHARACTERISTICS        | 105 |

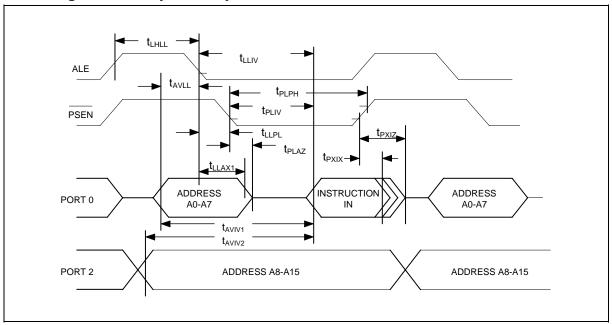

|     | 23.5  | Program Memory Read Cycle                              | 107 |

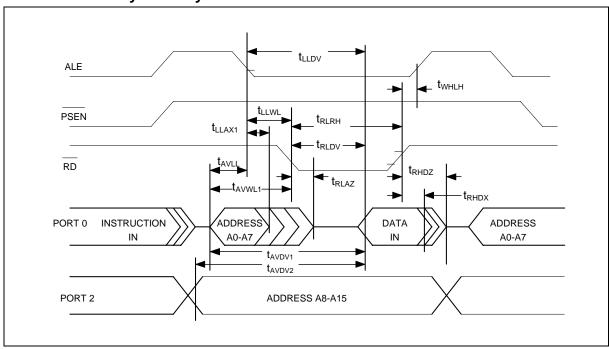

|     | 23.6  | Data Memory Read Cycle                                 | 107 |

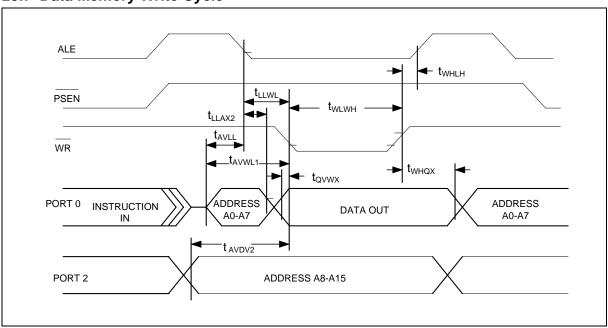

|     | 23.7  | Data Memory Write Cycle                                | 108 |

| 24. | TYPIC | CAL APPLICATION CIRCUITS                               | 109 |

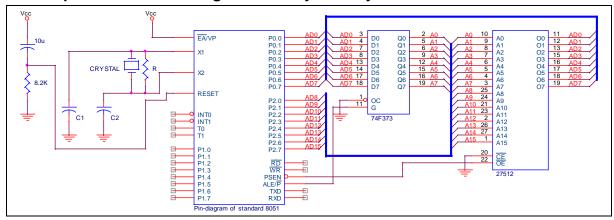

|     | 24.1  | Expanded External Program Memory and Crystal           | 109 |

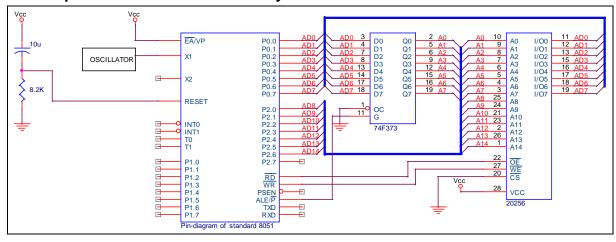

|     | 24.2  | Expanded External Data Memory and Oscillator           | 109 |

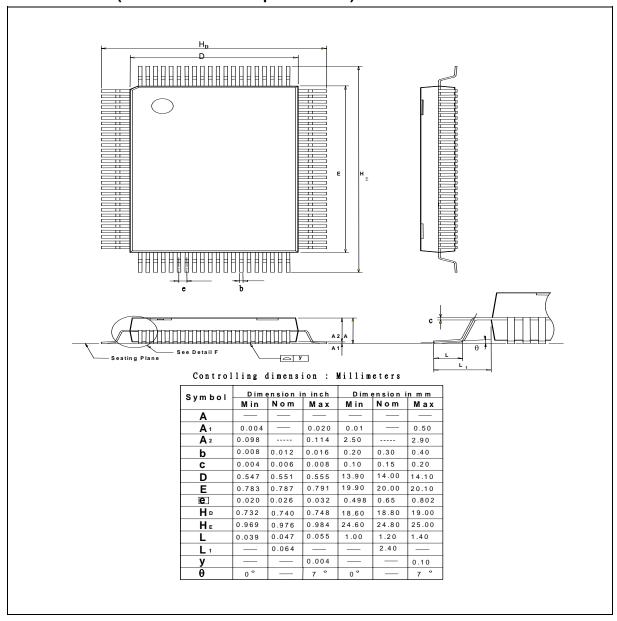

| 25. | PACK  | (AGE DIMENSIONS                                        | 110 |

|     | 25.1  | 100L QFP(14x20x2.75mm footprint 4.8mm)                 | 110 |

| 26. | APPL  | ICATION NOTE                                           | 111 |

| 27. | VERS  | SION HISTORY                                           | 117 |

- 3 -

### 1. GENERAL DESCRIPTION

The W79E658 is a fast, 8051/52-compatible microcontroller with a redesigned processor core that eliminates wasted clock and memory cycles. Typically, the W79E658 executes instructions 1.5 to 3 times faster than that of the traditional 8051/52, depending on the type of instruction, and the overall performance is about 2.5 times better at the same crystal speed. As a result, with the fully-static CMOS design, the W79E658 can accomplish the same throughput with a lower clock speed, reducing power consumption.

The W79E658 provides 256 bytes of on-chip RAM; 1-KB of auxiliary RAM; seven 8-bit, bi-directional and bit-addressable I/O ports; an additional 4-bit port P4; three 16-bit timer/counters; an UART serial port, 2 channels of I2C with master/slave capability and 8 channels of 10-bit ADC. These peripherals are all supported by ten interrupt sources with 2 levels of priority.

The W79E658 contains a 128-KB Flash EPROM whose contents may be updated in-system by a loader program stored in an auxiliary, 4-KB Flash EPROM. Once the contents are confirmed, it can be protected for security.

### 2. FEATURES

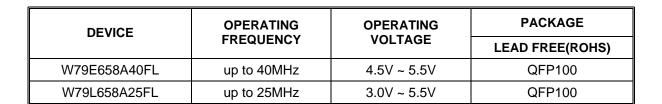

- Fully-static-design 8-bit Turbo 51 CMOS microcontroller up to 40MHz

- 128-KB of in-system-programmable Flash EPROM (AP Flash EPROM with ISP)

- 4-KB of Auxiliary Flash EPROM for the loader program (LD Flash EPROM)

- 1-KB auxiliary RAM, software-selectable, accessed by MOVX instruction

- 256 bytes of scratch-pad RAM

- Seven 8-bit bi-directional ports; Port 0 has internal pull-up resisters enabled by software.

- All pins with Schmitt trigger inputs

- One 4-bit multipurpose I/O port4 with Chips select(CS) and boot function

- Three 16-bit timers

- 6 channels of 8-bit PWM

- One enhanced full-duplex UART with framing-error detection and automatic address recognition

- 2-channels of I2C with master/slave capability

- 10-bit ADC with 8-channel inputs

- Software programmable access cycle to external RAM/peripherals

- 10 interrupt sources with two levels of priority

- Software reset function

- Optional H/L state of ALE/PSEN during power down mode

- Built-in power management

- Code protection

- Development tool

- JTAG ICE(In Circuit Emulator) tool

- Packages:

- Lead Free(RoHS) QFP 100: W79E658A40FL, W79L658A25FL

**Tables winbond seems**

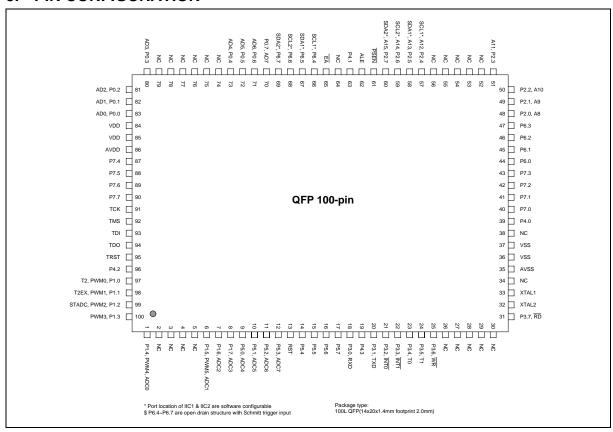

### 3. PIN CONFIGURATION

- 5 -

# massa winbond sassa

### 4. PIN DESCRIPTION

| SYMBOL           | TYPE <sup>1</sup> | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                        |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒĀ               | I                 | <b>EXTERNAL ACCESS ENABLE:</b> This pin forces the processor to execute the external ROM. The ROM address and data are not presented on the bus if the $\overline{EA}$ pin is high.                                                                                                                                                 |

| PSEN             | ОН                | PROGRAM STORE ENABLE: PSEN enables the external ROM data in the Port 0 address/data bus. When internal ROM access is performed, no PSEN strobe signal outputs originate from this pin.                                                                                                                                              |

| ALE              | ОН                | <b>ADDRESS LATCH ENABLE:</b> ALE enables the address latch that separates the address from the data on Port 0.                                                                                                                                                                                                                      |

| RST              | IL                | <b>RESET:</b> Set this pin high for two machine cycles while the oscillator is running to reset the device.                                                                                                                                                                                                                         |

| XTAL1            | I                 | CRYSTAL 1: Crystal oscillator input or external clock input.                                                                                                                                                                                                                                                                        |

| XTAL2            | 0                 | CRYSTAL 2: Crystal oscillator output.                                                                                                                                                                                                                                                                                               |

| $V_{SS}$         | I                 | GROUND: ground potential.                                                                                                                                                                                                                                                                                                           |

| $V_{DD}$         | I                 | POWER SUPPLY: Supply voltage for operation.                                                                                                                                                                                                                                                                                         |

| AV <sub>SS</sub> | I                 | Analog GROUND: for ADC                                                                                                                                                                                                                                                                                                              |

| $AV_{DD}$        | I                 | Analog Power Supply: for ADC                                                                                                                                                                                                                                                                                                        |

| P0.0-P0.7        | I/O<br>DSH        | <b>PORT 0:</b> 8-bit, open-drain, bi-directional I/O port. Port 0 has internal pull-up resisters enabled by setting bit 0 in A2h. This port also provides a multiplexed, low-order address / data bus during accesses to external memory.                                                                                           |

| P1.0-P1.7        | I/O<br>S H        | PORT 1: 8-bit, bi-directional I/O port with internal pull-up resistors. This port also provides alternate functions as below. P1.0 ~ P1.5 provide PWM0 ~ PWM5. P1.4 ~ P1.7 provide ADC0 ~ ADC3. P1.0 alternately provides Timer2 external count input.(T2) P1.1 alternately provides Timer2 Reload/Capture/Direction control.(T2Ex) |

| P2.0-P2.7        | I/O<br>S H        | <b>PORT 2:</b> 8-bit, bi-directional I/O port with internal pull-ups. This port also provides the upper address bits when accessing external memory. P2.4 to P2.7 can be software configured as I2C serial ports                                                                                                                    |

|                  | I/O               | PORT 3: 8-bit, bi-directional I/O port with internal pull-up resistors.  All bits have alternate functions, which are described below:  RXD (P3.0): Serial Port 0 input  TXD (P3.1): Serial Port 0 output  INTO (P3.2): External Interrupt 0                                                                                        |

| P3.0-P3.7        | SH                | INT1(P3.3): External Interrupt 1 T0 (P3.4):Timer 0 External Input T1 (P3.5):Timer 1 External Input WR (P3.6): External Data Memory Write Strobe RD (P3.7): External Data Memory Read Strobe                                                                                                                                         |

PIN DESCRIPTION, continued

| SYMBOL            | TYPE       | DESCRIPTIONS                                                                                                                                                                              |

|-------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D4 0 D4 2         | I/O        | PORT 4: 4-bit bi-directional I/O port. The P4.3 also provides the alternate                                                                                                               |

| P4.0-P4.3         | SH         | function REBOOT which is H/W reboot from LD flash.                                                                                                                                        |

| P5.0-P5.7         | I/O H      | <b>PORT 5:</b> A bi-directional I/O port with internal pull-ups. This port is not bit-addressable. The alternate functions of P5.0 to P5.3 are inputs of ADC4 to ADC7.                    |

| P6.0-P6.7         | I/O<br>D H | <b>PORT 6:</b> A bi-directional I/O port with internal pull-ups. This port is not bit-addressable. Pins P6.4 to P6.7 are open drain type and can be software configured as the I2C ports. |

| P7.0-P7.7         | I/O H      | <b>PORT 7:</b> A bi-directional I/O port with internal pull-ups. This port is not bit-addressable.                                                                                        |

| TCK <sup>2</sup>  | ΙH         | Used in debug mode with internal pull-up                                                                                                                                                  |

| TMS <sup>2</sup>  | ΙH         | Used in debug mode with internal pull-up                                                                                                                                                  |

| TDI <sup>2</sup>  | ΙH         | Used in debug mode with internal pull-up                                                                                                                                                  |

| TDO <sup>2</sup>  | OL         | Used in debug mode with internal weakly pull-low                                                                                                                                          |

| TRST <sup>2</sup> | ΙH         | Used in debug mode with internal pull-up                                                                                                                                                  |

Note:

- 1. TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain S: Schmitt Trigger

- 2. Keep debug pins in NC(no connection) if chip is not in debug mode.

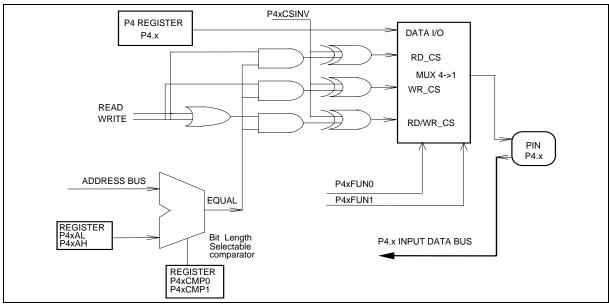

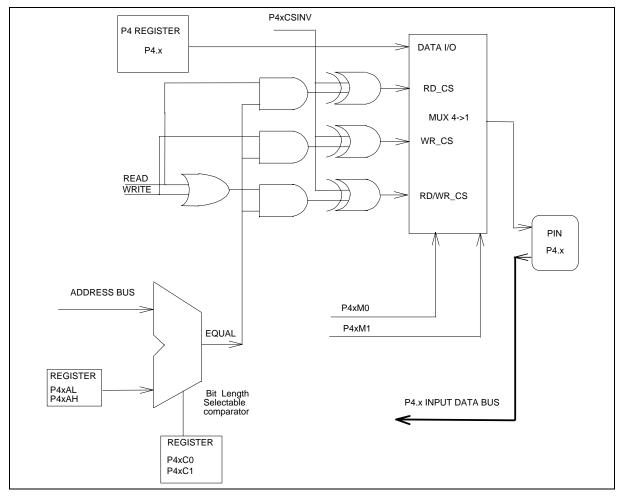

### 4.1 Port 4

SFR P4 at address A5H, is a 4-bit multipurpose programmable I/O port which functions are I/O, insert wait function and chip-select function. The Port 4 has four different operation modes:

In mode 0, P4.0  $\sim$  P4.3 is a 4-bit bi-directional I/O port which is the same as port 1. The default Port 4 is a general I/O function.

In mode1, P4.0 ~ P4.3 are read data strobe signals which are synchronized with  $\overline{RD}$  signal at specified addresses. These read data strobe signals can be used as chip-select signals for external peripherals.

In mode2, P4.0  $\sim$  P4.3 are write data strobe signals which are synchronized with  $\overline{\text{WR}}$  signal at specified addresses. These write data strobe signals can be used as chip-select signals for external peripherals.

In mode3, P4.0  $\sim$  P4.3 are read/write data strobe signals which are synchronized with  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$  signal at specified addresses. These read/write data strobe signals can be used as chip-select signals for external peripherals.

In mode1~mode3, Port 4 is configured with the feature of chip-select signals, the address range for chip-select signals depends on the contents of registers P4xAH and P4xAL, which contain the high-order byte and low-order byte, respectively, of the 16-bit address comparator for P4.x. The registers P4CONA and P4CONB contain the control bits to configure the Port 4 operation mode. This is illustrated in the following schematic.

Publication Release Date: December 24, 2007 - 7 - Revision A2.0

# s winbond sees

Figure 4-1

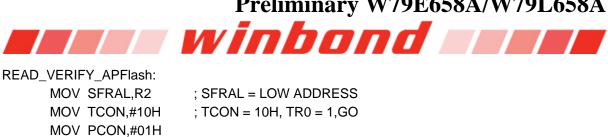

For example, the following program sets up P4.0 as a write-strobe signal for I/O port addresses 1234H – 1237H with positive polarity, while P4.1 – P4.3 are used as general I/O ports.

MOV P40AH, #12H

MOV P40AL, #34H ; Base I/O address 1234H for P4.0

MOV P4CONA, #00001010B ; P4.0 is a write-strobe signal; address lines A0 and A1 are masked.

MOV P4CONB, #00H ; P4.1 – P4.3 are general I/O ports

MOV P2ECON, #10H ; Set P40SINV to 1 to invert the P4.0 write-strobe to positive polarity.

Then, any instruction MOVX @DPTR, A (where DPTR is in 1234H – 1237H) generates a positive-polarity, write-strobe signal on pin P4.0, while the instruction MOV P4, #XX puts bits 3 – 1 of data #XX on pins P4.3 – P4.1.

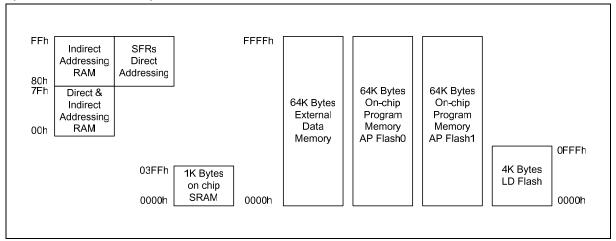

### 5. MEMORY ORGANIZATION

The W79E658 separates the memory into two separate sections, the Program Memory and the Data Memory. Program Memory stores instruction op-codes, while Data Memory stores data or memory-mapped devices.

### 5.1 Program Memory (on-chip Flash)

The Program Memory on the standard 8052 can only be addressed to 64 Kbytes long. By invoking the banking methodology, W79E633 can extend to two 64KB flash EPROM banks, AP Flash0 (AP0) and AP Flash1 (AP1). All instructions are fetched from this area, and the MOVC instruction can also access this region. There is an auxiliary 4-KB Flash EPROM (LD Flash EPROM), where the loader program for In-System Programming (ISP) resides. Both AP Flash banks are re-programmed by serial or parallel download according to this loader program.

The default active bank is AP0. User can set the EN128K bit to switch from AP0 to AP1 as well as properly set DCP1[2:0] to select one pin of Port1 to be the A16 to access the AP1 address region.

### **ROM Banking Control**

| Bit: | 7 | 6 | 5 | 4 | 3      | 2     | 1     | 0     |

|------|---|---|---|---|--------|-------|-------|-------|

|      | - | - | - | - | EN128K | DCP12 | DCP11 | DCP10 |

Mnemonic: ROMCON Address: ABh

EN128K On-chip ROM banking enable. Set this bit to enable AP Flash0 and AP Flash1 by banking mechanism. The P1.x is selected to be the auxiliary highest address line A16.

DCP1[2:0] A16 selection. By default, P1.7 is defined as A16.

| A16       | P1.0 | P1.1 | P1.2 | P1.3 | P1.4 | P1.5 | P1.6 | P1.7 |

|-----------|------|------|------|------|------|------|------|------|

| DCP1[2:0] | 000  | 001  | 010  | 011  | 100  | 101  | 110  | 111  |

Publication Release Date: December 24, 2007 - 9 - Revision A2.0

### 5.2 Data Memory

The W79E658 can access up to 64Kbytes of external Data Memory. This memory region is accessed by the MOVX instructions. Unlike the 8051 derivatives, the W79E658 contains on-chip 1K-bytes of Data Memory, which only can be accessed by MOVX instructions. The 1-Kbytes of SRAM located between address 0000h and 03FFh is enabled by setting DMEO bit of PMR register. If MOVX instruction accesses the addresses greater than 03FFh CPU will automatically access external memory through Port 0 and 2. In default condition the 1K-bytes SRAM is disabled and any MOVX directed to the space between 0000h and FFFFh goes to the expanded bus on the Port 0 and 2. The W79E658 also has the standard 256 bytes of on-chip Scratchpad RAM. This can be accessed either by direct addressing or by indirect addressing. There are also some Special Function Registers (SFRs), which can only be accessed by direct addressing. Since the Scratchpad RAM is only 256 bytes, it can be used only when data contents are small.

Figure 5-1 Memory Map

### 6. SPECIAL FUNCTION REGISTERS

The W79E658 uses Special Function Registers (SFR) to control and monitor peripherals. The SFR reside in register locations 80-FFh and are only accessed by direct addressing. The W79E658 contains all the SFR present in the standard 8051/52, as well as some additional SFR, and, in some cases, unused bits in the standard 8051/52 have new functions. SFR whose addresses end in 0 or 8 (hex) are bit-addressable. The following table of SFR is condensed, with eight locations per row. Empty locations indicate that there are no registers at these addresses. When a bit or register is not implemented, it reads high.

Table 6-1 Special Function Register Location Table

| F8 | EIP        | I2CON2 | I2ADDR20 | I2ADDR21 | I2DATA2     | I2STATUS2 | I2CLK2  | I2TIMER2 |

|----|------------|--------|----------|----------|-------------|-----------|---------|----------|

| F0 | В          |        |          |          |             |           |         |          |

| E8 | EIE        | I2CON  | I2ADDR10 | I2ADDR11 | I2DATA      | I2STATUS  | I2CLK   | I2TIMER  |

| E0 | ACC        |        |          |          |             |           |         |          |

| D8 | WDCON      | PWMP   | PWM0     | PWM1     | PWMCON<br>1 | PWM2      | PWM3    |          |

| D0 | PSW        |        |          |          |             |           |         | WDCON2   |

| C8 | T2CON      | T2MOD  | RCAP2L   | RCAP2H   | TL2         | TH2       | PWMCON2 | PWM4     |

| C0 | ADDCO<br>N | ADCL   | ADCH     | PWM5     | PMR         | STATUS    | ADCPS   | TA       |

| B8 | IP         | SADEN  |          |          |             |           |         |          |

| В0 | P3         | P5     | P6       | P7       |             |           |         |          |

| A8 | IE         | SADDR  |          | ROMCON   | SFRAL       | SFRAH     | SFRFD   | SFRCN    |

| Α0 | P2         | XRAMAH | P4CSIN   |          |             | P4        |         |          |

| 98 | SCON       | SBUF   | P42AL    | P42AH    | P43AL       | P43AH     |         | CHPCON   |

| 90 | P1         |        | P4CONA   | P4CONB   | P40AL       | P40AH     | P41AL   | P41AH    |

| 88 | TCON       | TMOD   | TL0      | TL1      | TH0         | TH1       | CKCON   |          |

| 80 | P0         | SP     | DPL      | DPH      |             |           |         | PCON     |

<sup>1.</sup> The SFRs in the column with dark borders are bit-addressable

- 11 -

Publication Release Date: December 24, 2007 Revision A2.0

<sup>2.</sup> The table is condensed with eight locations per row. Empty locations indicate that these are no registers at these addresses. When a bit or register is not implemented, it will read high.

Table 6-2 Special Function Registers

| SYMBOL    | DEFINITION                  | ADDR<br>ESS | M          | SB E        | BIT_AD     | DRES         | S, SYM       | BOL          | L             | SB            | RESET          |

|-----------|-----------------------------|-------------|------------|-------------|------------|--------------|--------------|--------------|---------------|---------------|----------------|

| I2TIMER2  | I2C2 Timer Counter Register | FFH         | -          | -           | -          | -            | -            | ENTI2        | DIV42         | TIF2          | 0000<br>0000B  |

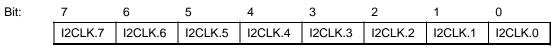

| I2CLK2    | I2C2 Clock Rate             | FEH         | I2CLK.7    | I2CLK.6     | I2CLK.5    | I2CLK.4      | I2CLK.3      | I2CLK.2      | I2CLK.1       | I2CLK.0       | 0000<br>0000B  |

| I2STATUS2 | I2C2 Status Register        | FDH         |            |             |            |              |              | -            | -             | -             | 0000<br>0000B  |

| I2DAT2    | I2C2 Data                   | FCH         | I2DAT.7    | I2DAT.6     | I2DAT.5    | I2DAT.4      | I2DAT.3      | I2DAT.2      | I2DAT.1       | I2DAT.0       | xxxx<br>xxxxxB |

| I2ADDR21  | I2C2 Slave Address1         | FBH         | ADDR.7     | ADDR.6      | ADDR.5     | ADDR.4       | ADDR.3       | ADDR.2       | ADDR.1        | -             | xxxx<br>xxxxxB |

| I2ADDR20  | I2C2 Slave Address0         | FAH         | ADDR.7     | ADDR.6      | ADDR.5     | ADDR.4       | ADDR.3       | ADDR.2       | ADDR.1        | GC            | xxxx<br>xxxx0B |

| I2CON2    | I2C2 Control Register       | F9H         | -          | ENS2        | STA        | STO          | SI           | AA           | -             | PSEL2         | x000<br>00x0B  |

| EIP       | Extended Interrupt Priority | F8H         | (FF)<br>-  | (FE)<br>-   | (FD)<br>-  | (FC)<br>PWDI | (FB)<br>-    | (FA)<br>-    | (F9)<br>PI2C2 | (F8)<br>PI2C1 | 0000<br>0000B  |

| PCH       | PC Counter high register    | F2H         |            |             |            |              |              |              |               |               | 00000000B      |

| PCL       | PC Counter low register     | F1H         |            |             |            |              |              |              |               |               | 0000000B       |

| В         | B Register                  | F0H         | (F7)       | (F6)        | (F5)       | (F4)         | (F3)         | (F2)         | (F1)          | (F0)          | 0000<br>0000B  |

| I2TIMER   | I2C1 Timer Counter Register | EFH         | -          | -           | -          | -            | -            | ENTI         | DIV4          | TIF           | 0000<br>0000B  |

| I2CLK     | I2C1 Clock Rate             | EEH         | I2CLK.7    | I2CLK.6     | I2CLK.5    | I2CLK.4      | I2CLK.3      | I2CLK.2      | I2CLK.1       | I2CLK.0       | 0000<br>0000B  |

| I2STATUS  | I2C1 Status Register        | EDH         |            |             |            |              |              | -            | -             | -             | 0000<br>0000B  |

| I2DAT     | I2C1 Data                   | ECH         | I2DAT.7    | I2DAT.6     | I2DAT.5    | I2DAT.4      | I2DAT.3      | I2DAT.2      | I2DAT.1       | I2DAT.0       | xxxx<br>xxxxxB |

| I2ADDR11  | I2C1 Slave Address1         | EBH         | ADDR.7     | ADDR.6      | ADDR.5     | ADDR.4       | ADDR.3       | ADDR.2       | ADDR.1        | -             | xxxx<br>xxxxxB |

| I2ADDR10  | I2C1 Slave Address0         | EAH         | ADDR.7     | ADDR.6      | ADDR.5     | ADDR.4       | ADDR.3       | ADDR.2       | ADDR.1        | GC            | xxxx<br>xxxx0B |

| I2CON     | I2C1 Control Register       | E9H         | -          | ENS1        | STA        | STO          | SI           | AA           | -             | -             | x000<br>00x0B  |

| EIE       | Extended Interrupt Enable   | E8H         | (EF)<br>-  | (EE)<br>-   | (ED)<br>-  | (EC)<br>EWDI | (EB)<br>-    | (EA)<br>-    | (E9)<br>EI2C2 | (E8)<br>EI2C1 | 0000<br>0000B  |

| ACC       | Accumulator                 | E0H         | (E7)       | (E6)        | (E5)       | (E4)         | (E3)         | (E2)         | (E1)          | (E0)          | 0000<br>0000B  |

| PWM3      | PWM3 Output                 | DEH         |            |             |            |              |              |              |               |               | 0000<br>0000B  |

| PWM2      | PWM2 Output                 | DDH         |            |             |            |              |              |              |               |               | 0000<br>0000B  |

| PWMCON1   | PWM Control Register1       | DCH         | PWM3O<br>E | PWM2O<br>E  | ENPWM<br>3 | ENPWM<br>2   | PWM1O<br>E   | PWM0O<br>E   | ENPWM<br>1    | ENPWM<br>0    | 0000<br>0000B  |

| PWM1      | PWM1 Output                 | DBH         |            |             |            |              |              |              |               |               | 0000<br>0000B  |

| PWM0      | PWM0 Output                 | DAH         |            |             |            |              |              |              |               |               | 0000<br>0000B  |

| PWMP      | PWM Pre-scale Register      | D9H         |            |             |            |              |              |              |               |               | 0000<br>0000B  |

| WDCON     | Watch-Dog Control           | D8H         | (DF)<br>-  | (DE)<br>POR | (DD)<br>-  | (DC)<br>-    | (DB)<br>WDIF | (DA)<br>WTRF | (D9)<br>EWT   | (D8)<br>RWT   | 0100<br>0000B  |

| WDCON2    | Watch-Dog Control2          | D7H         | -          | -           | -          | -            | -            | -            | -             | STRLD         | 0000<br>0000B  |

| PSW       | Program Status Word         | D0H         | (D7)       | (D6)        | (D5)       | (D4)         | (D3)         | (D2)         | (D1)          | (D0)          | 0000           |

# sees winbond sees

Table 6-3 Special Function Registers, continued

| SYMBOL  | DEFINITION                        | ADD<br>RESS | М           | SB E         | BIT_AD       | DRES         | S, SYM        | BOL          | LS           | В              | RESET          |

|---------|-----------------------------------|-------------|-------------|--------------|--------------|--------------|---------------|--------------|--------------|----------------|----------------|

| PWM4    | PWM4 Output                       | CFH         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| PWMCON2 | PWM Control Register 2            | CEH         | -           | -            | -            | -            | PWM5O<br>E    | PWM4O<br>E   | ENPWM<br>5   | ENPW<br>M4     | 0000<br>0000B  |

| TH2     | T2 reg. High                      | CDH         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| TL2     | T2 reg. Low                       | ссн         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| RCAP2H  | T2 Capture Low                    | СВН         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| RCAP2L  | T2 Capture High                   | CAH         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| T2MOD   | Timer 2 Mode                      | C9H         | -           | -            | -            | -            | T2CR          | -            | -            | DCEN           | xxxx 0xx0E     |

| T2CON   | Timer 2 Control                   | C8H         | (CF)<br>TF2 | (CE)<br>EXF2 | (CD)<br>RCLK | (CC)<br>TCLK | (CB)<br>EXEN2 | (CA)<br>TR2  | (C9)<br>C/T2 | (C8)<br>CP/RL2 | 0000<br>0000B  |

| TA      | Time Access Register              | C7H         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| ADCPS   | ADC Input Pin Switch              | C6H         | ADCPS.      | ADCPS.<br>6  | ADCPS.<br>5  | ADCPS.       | ADCPS.        | ADCPS.<br>2  | ADCPS.       | ADCPS.         | 0000<br>0000B  |

| STATUS  | Status Register                   | C5H         | -           | HIP          | LIP          | -            | -             | -            | -            | -              | x00x xxxxE     |

| PMR     | Power Management Register         | C4H         | -           | -            | -            | -            | -             | ALEOF<br>F   | -            | DME0           | xxxx x0x0E     |

| PWM5    | PWM5 Output                       | СЗН         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| ADCH    | ADC converter Result High<br>Byte | C2H         | ADC.9       | ADC.8        | ADC.7        | ADC.6        | ADC.5         | ADC.4        | ADC.3        | ADC.2          | xxxx<br>xxxxxB |

| ADCL    | ADC converter Result Low<br>Byte  | C1H         | ADCLK1      | ADCLK<br>0   | -            | -            | -             | -            | ADC.1        | ADC.0          | 00xx<br>xxxxxB |

| ADCCON  | ADC Control Register              | C0H         | ADCEN       | -            | ADCEX        | ADCI         | ADCS          | AADR2        | AADR1        | AADR0          | 0x000000E      |

| SADEN   | Slave Address Mask                | В9Н         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| IP      | Interrupt Priority                | В8Н         | (BF)<br>-   | (BE)<br>PADC | (BD)<br>PT2  | (BC)<br>PS   | (BB)<br>PT1   | (BA)<br>PX1  | (B9)<br>PT0  | (B8)<br>PX0    | x000<br>0000B  |

| P7      | Port 7                            | взн         |             |              |              |              |               |              |              |                | 1111<br>1111B  |

| P6      | Port 6                            | В2Н         |             |              |              |              |               |              |              |                | 1111<br>1111B  |

| P5      | Port 5                            | B1H         |             |              |              |              |               |              |              |                | 1111<br>1111B  |

| P3      | Port 3                            | вон         | (B7)<br>RD  | (B6)<br>WR   | (B5)<br>T1   | (B4)<br>T0   | (B3)<br>INT1  | (B2)<br>INT0 | (B1)<br>TXD  | (B0)<br>RXD    | 1111<br>1111B  |

| SFRCN   | F/W Flash Control                 | AFH         | BANK        | WFWIN        | NOE          | NCE          | CTRL3         | CTRL2        | CTRL1        | CTRL0          | 0011<br>1111B  |

| SFRFD   | F/W Flash Data                    | AEH         |             |              |              |              |               |              |              |                | xxxx<br>xxxxxB |

| SFRAH   | F/W Flash High Address            | ADH         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| SFRAL   | F/W Flash Low Address             | ACH         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

| ROMCON  | ROM Control                       | ABH         | -           | -            | -            | -            | EN128K        | DCP12        | DCP11        | DCP10          | 00000111E      |

| SADDR   | Slave Address                     | А9Н         |             |              |              |              |               |              |              |                | 0000<br>0000B  |

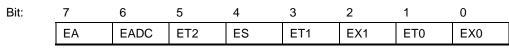

| IE      | Interrupt Enable                  | A8H         | (AF)<br>EA  | (AE)<br>EADC | (AD)<br>ET2  | (AC)<br>ES   | (AB)<br>ET1   | (AA)<br>EX1  | (A9)<br>ET0  | (A8)<br>EX0    | 0000<br>0000B  |

- 13 -

# as winbond sassa

Table 6-4 Special Function Registers, continued

| SYMBOL | DEFINITION                  | ADD<br>RESS | MS                   | SB E         | BIT_AD       | DRES         | S, SYM        | BOL           | LS           | ВВ          | RESET          |

|--------|-----------------------------|-------------|----------------------|--------------|--------------|--------------|---------------|---------------|--------------|-------------|----------------|

| P4     | Port 4                      | A5H         | -                    | -            | -            | -            |               |               |              |             | xxxx<br>1111B  |

| P4CSIN | P4 CS SIGN                  | A2H         | P43CSI<br>NV         | P42CSI<br>NV | P41CSI<br>NV | P40CSI<br>NV | -             | PWDNH         | RMWFP        | P0UP        | 0000<br>0000B  |

| XRAMAH | RAM High byte Address       | A1H         | -                    | -            | -            | -            | -             | -             | 0            | 0           | 0000<br>0000B  |

| P2     | Port 2                      | A0H         | (A7)<br>A15          | (A6)<br>A14  | (A5)<br>A13  | (A4)<br>A12  | (A3)<br>A11   | (A2)<br>A10   | (A1)<br>A9   | (A0)<br>A8  | 1111<br>1111B  |

| CHPCON | On chip Programming Control | 9FH         | SWRST/<br>REBOO<br>T | -            | LD/AP        | -            | 0             | 0             | LDSEL        | ENP         | 0000<br>0000B  |

| P43AH  | HI Addr. Comparator of P4.3 | 9DH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P43AL  | LO Addr. Comparator of P4.3 | 9CH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P42AH  | HI Addr. Comparator of P4.2 | 9BH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P42AL  | LO Addr. Comparator of P4.2 | 9AH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| SBUF   | Serial Buffer               | 99H         |                      |              |              |              |               |               |              |             | xxxx<br>xxxxxB |

| SCON   | Serial Control              | 98H         | (9F)<br>SM0/FE       | (9E)<br>SM1  | (9D)<br>SM2  | (9C)<br>REN  | (9B)<br>TB8   | (9A)<br>RB8   | (99)<br>TI   | (98)<br>RI  | 0000<br>0000B  |

| P41AH  | HI Addr. Comparator of P4.1 | 97H         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P41AL  | LO Addr. Comparator of P4.1 | 96H         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P40AH  | HI Addr. Comparator of P4.0 | 95H         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P40AL  | LO Addr. Comparator of P4.0 | 94H         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| P4CONB | P4 Control Register         | 93H         | P43FUN<br>1          | P43FUN<br>0  | P43CM<br>P1  | P43CM<br>P0  | P42FUN<br>1   | P42FUN<br>0   | P42CM<br>P1  | P42CM<br>P0 | 0000<br>0000B  |

| P4CONA | P4 Control Register         | 92H         | P41FUN<br>1          | P41FUN<br>0  | P41CM<br>P1  | P41CM<br>P0  | P40FUN<br>1   | P40FUN<br>0   | P40CM<br>P1  | P40CM<br>P0 | 0000<br>0000B  |

| P1     | Port 1                      | 90H         | (97)                 | (96)         | (95)         | (94)         | (93)<br>TXD_1 | (92)<br>RXD_1 | (91)<br>T2EX | (90)<br>T2  | 1111<br>1111B  |

| CKCON  | Clock Control               | 8EH         | WD1                  | WD0          | T2M          | T1M          | ТОМ           | MD2           | MD1          | MD0         | 0000<br>0001B  |

| TH1    | Timer High 1                | 8DH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| TH0    | Timer High 0                | 8CH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| TL1    | Timer Low 1                 | 8BH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| TL0    | Timer Low 0                 | 8AH         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| TMOD   | Timer Mode                  | 89H         | GATE                 | C/T          | M1           | МО           | GATE          | C/T           | M1           | МО          | 0000<br>0000B  |

| TCON   | Timer Control               | 88H         | (8F)<br>TF1          | (8E)<br>TR1  | (8D)<br>TF0  | (8C)<br>TR0  | (8B)<br>IE1   | (8A)<br>IT1   | (89)<br>IE0  | (88)<br>IT0 | 0000<br>0000B  |

| PCON   | Power Control               | 87H         | SMOD                 | SMOD0        | -            | -            | GF1           | GF0           | PD           | IDL         | 00xx<br>0000B  |

| DPH    | Data Pointer High           | 83H         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

| DPL    | Data Pointer Low            | 82H         |                      |              |              |              |               |               |              |             | 0000<br>0000B  |

#

Table 6-5 Special Function Registers, continued

| SYMBOL | DEFINITION    | ADD<br>RESS | MS   | SB E | BIT_AD | S, SYM | BOL  | LS   | RESET |      |               |

|--------|---------------|-------------|------|------|--------|--------|------|------|-------|------|---------------|

| SP     | Stack Pointer | 81H         |      |      |        |        |      |      |       |      | 0000<br>0111B |

| P0     | Port 0        | 80H         | (87) | (86) | (85)   | (84)   | (83) | (82) | (81)  | (80) | 1111<br>1111B |

Note: In column BIT\_ADDRESS, SYMBOL, containing ( ) item means the bit address.

#### PORT 0

Bit: 7 6 5 4 3 2 1 0

P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0

Mnemonic: P0 Address: 80h

Port 0 is an open-drain, bi-directional I/O port after chip is reset. Besides, it has internal pull-up resisters enabled by setting P0UP of A2H to high. This port also provides a multiplexed, low-order address/data bus when the W79E658 accesses external memory.

### **STACK POINTER**

Bit:

7

6

5

4

3

2

1

0

SP.7

SP.6

SP.5

SP.4

SP.3

SP.2

SP.1

SP.0

Mnemonic: SP Address: 81h

The Stack Pointer stores the address in Scratchpad RAM where the stack begins. It always points to the top of the stack.

### **DATA POINTER LOW**

Bit:

7

6

5

4

3

2

1

0

DPL.7

DPL.6

DPL.5

DPL.4

DPL.3

DPL.2

DPL.1

DPL.0

Mnemonic: DPL Address: 82h

This is the low byte of the standard-8051/52, 16-bit data pointer.

### **DATA POINTER HIGH**

Bit: 7 6 5 4 3 2 1 0

DPH.7 DPH.6 DPH.5 DPH.4 DPH.3 DPH.2 DPH.1 DPH.0

Mnemonic: DPH Address: 83h

This is the low byte of the standard-8051/52, 16-bit data pointer.

### **POWER CONTROL**

Bit: 7 6 5 4 3 2 1 0

SMOD SMOD0 - - GF1 GF0 PD IDL

Mnemonic: PCON Address: 87h

- 15 -

Publication Release Date: December 24, 2007 Revision A2.0

# massa winbond sassa

| BIT       | NAME                                                                                  | FUNCTION                                                                                                                                                                                                               |  |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7         | SMOD                                                                                  | 1: This bit doubles the serial-port baud rate in modes 1, 2 and 3.                                                                                                                                                     |  |  |  |  |  |  |

| 6         |                                                                                       | 0: Disable Framing Error Detection. SCON.7 acts as per the standard 8051/52 function.                                                                                                                                  |  |  |  |  |  |  |

| 6 SIVIODO |                                                                                       | 1: Enable Framing Error Detection. SCON.7 indicates a Frame Error and acts as the FE flag.                                                                                                                             |  |  |  |  |  |  |

| 5-4       | -                                                                                     | Reserved                                                                                                                                                                                                               |  |  |  |  |  |  |

| 3         | GF1                                                                                   | General-purpose user flag.                                                                                                                                                                                             |  |  |  |  |  |  |

| 2         | GF0                                                                                   | General-purpose user flag.                                                                                                                                                                                             |  |  |  |  |  |  |

| 1         | 1 PD 1: Go into POWER DOWN mode. In this mode, all clocks and program execut stopped. |                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 0         |                                                                                       | 1: Go into IDLE mode. In this mode, the CPU clock stops, so program execution stops too. However, the clock to the serial port, ADC, PWM timer and interrupt blocks does not stop, so these blocks continue operating. |  |  |  |  |  |  |

### **TIMER CONTROL**

Mnemonic: TCON Address: 88h

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7   | TF1  | Timer 1 overflow flag: This bit is set when Timer 1 overflows. It is cleared automatically when the program executes the Timer-1 interrupt service routine Software can also set or clear this bit.                                          |  |  |  |  |  |  |  |

| 6   | TR1  | Timer 1 run control: This bit turns the Timer 1 on or off by setting TR1 to 1 or 0.                                                                                                                                                          |  |  |  |  |  |  |  |

| 5   | TF0  | Timer 0 overflow flag: This bit is set when Timer 0 overflows. It is cleared automatically when the program executes the Timer-0 interrupt service routine. Software can also set or clear this bit.                                         |  |  |  |  |  |  |  |

| 4   | TR0  | Timer 0 run control: This bit turns Timer 0 on or off by setting TR0 to 1 or 0.                                                                                                                                                              |  |  |  |  |  |  |  |

| 3   | IE1  | Interrupt 1 Edge Detect: Set by hardware when an edge / level is detected on INT1. This bit is cleared by the hardware when the ISR is executed only if the interrupt is edge-triggered. Otherwise, it follows the pin.                      |  |  |  |  |  |  |  |

| 2   | IT1  | Interrupt 1 type control: Specify falling-edge or low-level trigger for $\overline{\text{INT1}}$ .                                                                                                                                           |  |  |  |  |  |  |  |

| 1   | IE0  | Interrupt 0 Edge Detect: Set by hardware when an edge / level is detected on $\overline{\text{INT0}}$ . This bit is cleared by the hardware when the ISR is executed only if the interrupt is edge-triggered. Otherwise, it follows the pin. |  |  |  |  |  |  |  |

| 0   | IT0  | Interrupt 0 type control: Specify falling-edge or low-level trigger for $\overline{\text{INT0}}$ .                                                                                                                                           |  |  |  |  |  |  |  |

### **TIMER MODE CONTROL**

Bit: 6 5 4 3 0 1 GATE M1 M0 GATE M1 M0  $C/\overline{T}$  $C/\overline{T}$ TIMER1 TIMER0

Mnemonic: TMOD Address: 89h

# **Esses winbond sesses**

| BIT    | NAME                                                                                                                                | FUNCTION                                                                                                                                   |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        |                                                                                                                                     | Gating control: When this bit is set, Timer 1 is enabled only while the INT1 pin is high                                                   |  |  |  |

| 7 GATE |                                                                                                                                     | and the TR1 control bit is set. When cleared, the INT1 pin has no effect, and Timer 1 is enabled whenever TR1 is set.                      |  |  |  |

| 6      | Timer or Counter Select: When clear, Timer 1 is incremented by the internal When set, the timer counts falling edges on the T1 pin. |                                                                                                                                            |  |  |  |

| 5      | M1                                                                                                                                  | Timer 1 mode select bit 1. See table below.                                                                                                |  |  |  |

| 4      | MO                                                                                                                                  | Timer 1 mode select bit 0. See table below.                                                                                                |  |  |  |

|        |                                                                                                                                     | Gating control: When this bit is set, Timer 0 is enabled only while the INTO pin is high                                                   |  |  |  |

| 3      | GATE                                                                                                                                | and the TR0 control bit is set. When cleared, the $\overline{\text{INT0}}$ pin has no effect, and Timer 0 is enabled whenever TR0 is set.  |  |  |  |

| 2      | C/T                                                                                                                                 | Timer or Counter Select: When clear, Timer 0 is incremented by the internal clock. When set, the timer counts falling edges on the T0 pin. |  |  |  |

| 1      | M1                                                                                                                                  | Timer 0 mode select bit 1. See table below.                                                                                                |  |  |  |

| 0      | MO                                                                                                                                  | Timer 0 mode select bit 0. See table below.                                                                                                |  |  |  |

#### M1, M0: Mode Select bits:

M1 M0 Mode

0 Mode 0: 8-bit timer/counter TLx serves as 5-bit pre-scale.

0 1 Mode 1: 16-bit timer/counter, no pre-scale.

1 0 Mode 2: 8-bit timer/counter with auto-reload from THx

1 1 Mode 3:

(Timer 0) TL0 is an 8-bit timer/counter controlled by the standard Timer-0 control bits. TH0 is an 8-bit timer only controlled by Timer-1 control bits.

(Timer 1) Timer/Counter 1 is stopped.

### TIMER 0 LSB

Bit: 7 6 5 4 3 2 1 0

TL0.7 TL0.6 TL0.5 TL0.4 TL0.3 TL0.2 TL0.1 TL0.0

Mnemonic: TL0 Address: 8Ah

TL0.7-0 Timer 0 LSB

### **TIMER 1 LSB**

Bit: 7 6 5 4 3 2 1 0

TL1.7 TL1.6 TL1.5 TL1.4 TL1.3 TL1.2 TL1.1 TL1.0

Mnemonic: TL1 Address: 8Bh

TL1.7-0 Timer 1 LSB

#### TIMER 0 MSB

Bit: 6 5 4 3 2 1 0 TH0.7 TH0.6 TH0.5 TH0.4 TH0.3 TH0.2 TH0.1 TH0.0

Mnemonic: TH0 Address: 8Ch

- 17 -

TH0.7-0 Timer 0 MSB

Publication Release Date: December 24, 2007 Revision A2.0

### **TIMER 1 MSB**

Bit:

7

6

5

4

3

2

1

0

TH1.7

TH1.6

TH1.5

TH1.4

TH1.3

TH1.2

TH1.1

TH1.0

Mnemonic: TH1 Address: 8Dh

TH1.7-0 Timer 1 MSB

### **CLOCK CONTROL**

Bit: 7 5 4 3 2 1 0 WD1 WD0 T2M T<sub>1</sub>M T0M MD2 MD1 MD0

Mnemonic: CKCON Address: 8Eh

| BIT                                                                     | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7                                                                       | WD1  | Vatchdog Timer mode select bit 1. See table below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 6                                                                       | WD0  | Watchdog Timer mode select bit 0. See table below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Timer 2 clock select:  5 T2M 1: divide-by-4 clock 0: divide-by-12 clock |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 4                                                                       | T1M  | Timer 1 clock select: 1: divide-by-4 clock 0: divide-by-12 clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 3                                                                       | ТОМ  | Timer 0 clock select: 1: divide-by-4 clock 0: divide-by-12 clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 2                                                                       | MD2  | Stretch MOVX select bit 2:  MD2, MD1, and MD0 select the stretch value for the MOVX instruction. The RD or R |  |  |  |  |  |

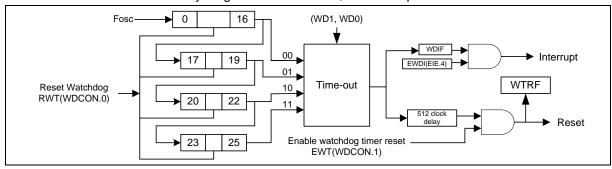

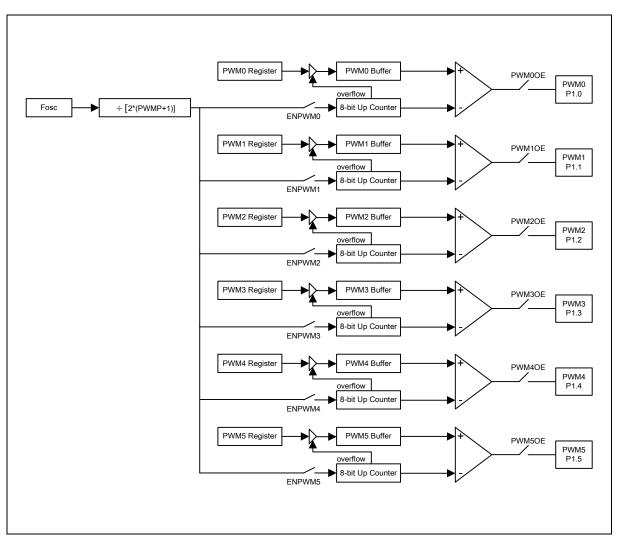

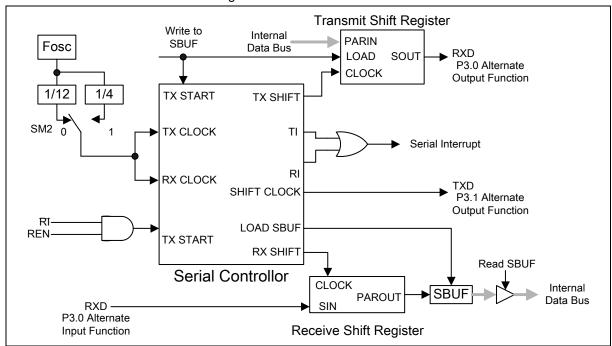

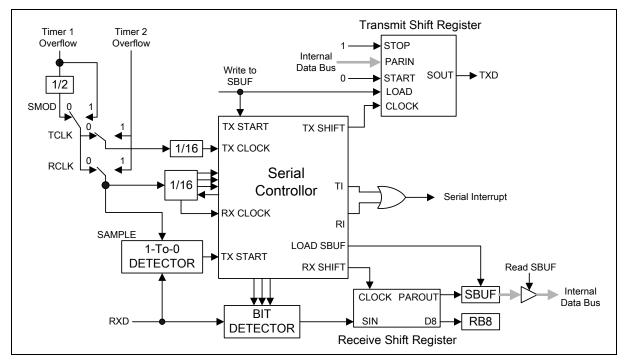

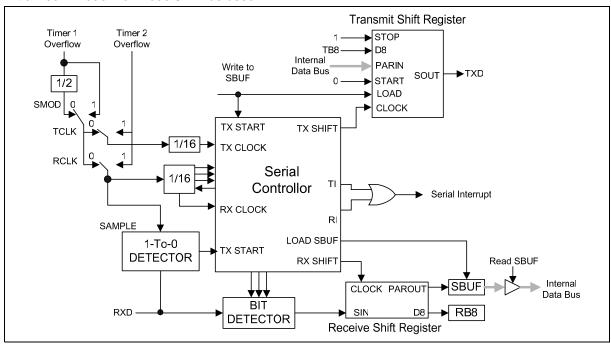

| 1                                                                       | MD1  | Stretch MOVX select bit 1. See MD2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |