#### Triscend Development Tools Update

### Triscend E5 Support

The Triscend E5 family of Configurable System-on-Chip (CSoC) devices is based on a performance accelerated 8-bit 805 I microcontroller. The E5 Family consists of several devices which vary in the amount of on-chip programmable logic, RAM, and I/O. The E5 is ideal for embedded systems applications that demand both fast time-to-market and high levels of customization.

Software development tools (assembler, ANSI C Compiler, and target debugger) from Keil Software fully support the E5 and provide a platform for programming and debugging your real-time, in-system target hardware.

#### Configurable System-on-Chip (CSoC)

Designers may configure E5 CSoC chips using the Triscend FastChip Development System. FastChip software customizes the processor's peripherals using a drag and drop methodology which allows you to create your own 805 I derivatives on-demand. Simply select the desired peripheral from the library and drag it into place. FastChip makes the rest of the process automatic so you can begin code development without worrying about the implementation details of the peripheral set.

#### JTAG Debugging with µVision2

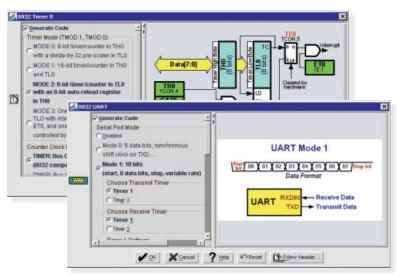

The Triscend E5 family supports target-level debugging via the built-in JTAG interface. Using the Triscend JTAG driver with the Keil  $\mu$ Vision2 Debugger, you may test application programs running on your actual target hardware.

The JTAG interface allows you to download program code, set breakpoints, watch memory locations, and single-step through your C or assembly programs. Since the JTAG interface works with the Keil debugger, you can instantly get started writing and testing embedded programs for the Triscend E5 family. The JTAG debugger gives you full access to the Triscend E5 peripherals.

| This Newsletter Contains Information About: |  |  |  |  |  |  |

|---------------------------------------------|--|--|--|--|--|--|

| The FastChip Design Flow Process            |  |  |  |  |  |  |

| Downloading a Design to the E5Page 4        |  |  |  |  |  |  |

| The Triscend E5 Development PlatformPage 5  |  |  |  |  |  |  |

| Using the Keil $\mu$ Vision2 IDEPage 6      |  |  |  |  |  |  |

| Using the Keil µVision2 DebuggerPage 7      |  |  |  |  |  |  |

| E5 Devices Available from Triscend          |  |  |  |  |  |  |

#### FastChip Design Flow (Part 1)

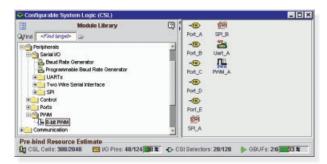

The Triscend E5 is a Configurable Systemon-Chip (CSoC) that you can easily customize to meet your target requirements. Using the FastChip software, you specify how to use the standard on-chip peripherals and select additional peripherals to include from the module library.

The following configuration example shows just how easy this is. To begin, start FastChip and create a new project.

## Select and Configure Standard Peripherals

Each E5 device has dedicated resources (peripherals) that are available. These include the default peripherals found on a standard 8051 microcontroller.

The first step in configuring your FastChip project is to select and configure the on-chip peripherals for your application. FastChip then writes the code necessary to initialize the peripherals you selected.

## **Drag and Drop Custom Peripherals**

FastChip comes with a large module library of additional peripherals you can drag and drop directly into your project. Choose from I/O Ports, Pulse Width Modulators, SPI, or whatever your target application requires.

# Configure and Connect Peripherals

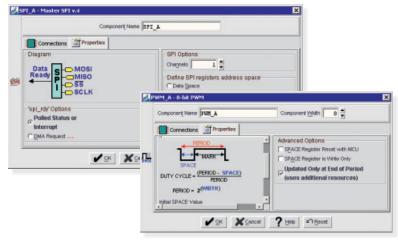

After you select the dedicated resources and add custom peripherals to your project, you must configure each peripheral and connect it to the E5.

Each peripheral from the module library provides a dialog where you may specify the names to use for I/O (connections) and define the characteristics (properties).

**Step 1**. Select the standard 8051 peripherals for your target E5 device.

**Step 2**. Drag and drop customized peripherals into your design.

**Step 3**. Connect peripherals, assign names, and select memory spaces.

#### **Generate Source Code**

After selecting and configuring the on-chip peripherals in your FastChip project, you may generate C or assembler source code to initialize them. The source code created by FastChip is fully documented and even includes definitions of the bits of each SFR (Special Function Register) that are used.

Code that is generated is fully compatible with the Keil 8051 C compiler and may easily be included in your  $\mu$ Vision2 projects.

#### **Assign I/O Pins**

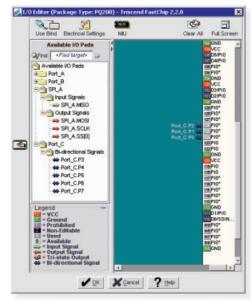

Most custom peripherals in your FastChip project require some form of input and output. Those that interact with external signals require that you connect pins on the E5 CSoC to the internal signals of the peripheral.

The I/O Editor shows unassigned I/O pads of custom peripherals in the left window and pins of the E5 device in the right window. Using the editor, FastChip allows you to simply drag and drop the peripheral's signal name onto the desired E5 pin to make that connection.

As signals are connected, they are annotated using the symbols shown in the legend at the bottom left.

#### **Bind Your Design**

Before you can download your design to the E5 device, you must bind the design to the device's resources. The binding process determines the configuration information FastChip will download to the E5.

When you bind your project, you may specify the amount of effort FastChip expends.

During the bind process, FastChip displays status, errors, warnings, and a summary. If there are problems that prevent the design from being bound, you may correct them and re-bind the project.

```

ADDRESS H

BEGIN SOFT HODULE REGISTER DECLARATIONS

CHAR_XDATA (UART2_Data_Register_RXTXbuf,@xeff5)

CHRR XDATE (URRIZ Data Register Moder Control, 0xeff6)

CHRR XDATE (URRIZ Data Register Moder Status, 0xeff6)

CHRR XDATE (URRIZ Data Register Moder Status, 0xeff7)

CHRR XDATE (URRIZ Data Register Moder Status, 0xeff7)

CHRR XDATE (URRIZ Data Ref)/ IE (Address 0xe8)

CHRR XDATE (SPI1 Data Ref)/

CHRR XDATE (SPI1 D

INIT.C

7 | 6 | 5 | 4 | 3 | 2 | 1 |

CHAR_XDATA (SP12_Data_Rec//

CHAR_ARRAY_XDATA (SP12_Cd//

| ET2 | ES | ET1 | EX1 | ET0 | EX0 |

CHAR_XDATA (port1,0xeff0)//

CHAR_XDATA (port2,0xefef)

CHAR XDATA (Port3, 0xefee) //

CHAR_XDATA (PORT4, Exefed)

CHAR_XDATA (Port5,0xefec

TR8 - 0;

// Disable Timer 8 (TCON.4)

TMOD &= BxF0;

TMOD |= 8x89;

// Clear Timer 0 bits (lower mibb)

// Set appropriate bits for Timer

---- END SOFT MODULE

0×88;

// Set Timer 0 low byte to user-de

// Set Timer 0 high byte to user-de

THB = 0x88;

CKCON &- BxF7; // Timer 0 clock source is (BusClock

ET8 - 0:

// Set or clear Timer 0 interrupt (IE

```

**Step 4**. FastChip automatically generates initialization source code.

Step 5. Assign I/O Pins using the I/O Editor.

**Step 6**. Bind your design to the E5 device.

## Combine Logic and Firmware

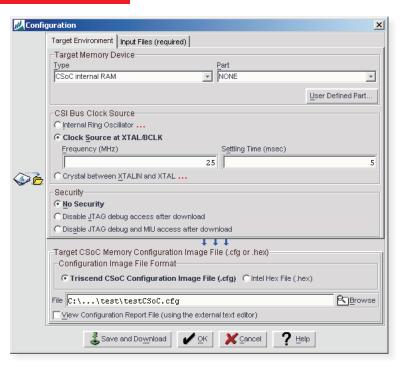

When you are finished with your design, FastChip combines the logic and firmware and downloads them to your target system. You must specify the path of the Target CSoC memory configuration, the path of the CSL configuration file generated during the Bind Process, and the Intel HEX file (firmware) generated by the Keil tools.

Before downloading, you may configure the Target Memory Device, the CSI Bus Clock source and speed, and the type of security.

The download process is automatic. All the necessary files, logic, and firmware are transferred to the target via the on-chip JTAG interface.

## Your Custom 805 I is Ready to Use

And, voila! Your customized 8051 CSoC system is now ready to use.

#### **Debug and Test**

Debugging and testing an embedded CSoC application is extremely easy due to tight integration with the Keil Software  $\mu$ Vision2 Debugger. Using the Keil tools, you may immediately start debugging your target application on the actual hardware using the Triscend Debugger Driver (for  $\mu$ Vision2) and the on-chip JTAG interface.

Combining the ease and simplicity of the FastChip design software with the flexibility of the Keil  $\mu$ Vision2 IDE provides a robust CSoC development environment.

#### How To Get FastChip

Visit www.triscend.com to download a fully-functional evaluation version of FastChip and get started designing your CSoC-based system today.

**Step 7**. Combine the configuration logic and firmware and download.

Step 8. Your customized 8051 is ready.

Step 9. Debug and test your target application.

#### Triscend E5 Development Platform

#### **Getting Started**

The best way to start your own CSoC project is to get the Triscend E5 Development Kit. This kit includes the E5 evaluation board that is designed to help you create working programs using the E5 family of devices. All features of the board are fully supported by FastChip and  $\mu$ Vision2.

The E5 Development Kit provides a flexible and powerful platform for quickly creating, developing, and debugging embedded system designs based on the 8-bit E5 family of CSoC devices. It features the E5 evaluation board, the E5 base board, a power supply, and a parallel cable for download and debug.

- Triscend TE520 CSoC Device

- 128 KByte Flash Memory

- Serial Configuration EEPROM Socket

- 40 MHz Oscillator

- ITAG Debug and Download

- Two 7-segment Displays

- RS-232 Serial Channel

This complete kit is available from Triscend. For more details, visit **www.triscend.com**.

#### **Technical Support**

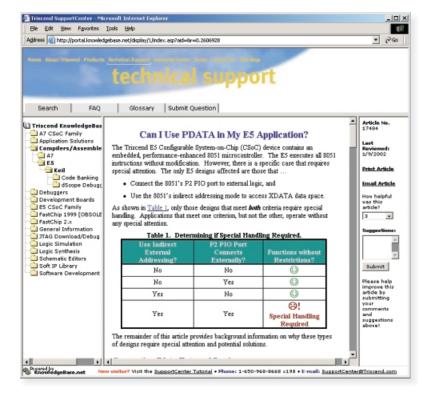

Both Keil and Triscend provide world-class technical support to help answer your development questions.

Triscend provides web-based technical support that is available 24 hours a day for. Their web site includes FAQ's as well as an indexed, searchable knowledge base of technical articles.

Keil Software offers a knowledgebase with over 1500 articles, dozens of application notes, download files, and a discussion forum you may utilize to answer your technical questions. For more information, visit www.keil.com/support.

The Triscend E5 Development Kit includes everything you need to get started.

Technical Support is available 24/7 from Triscend (www.triscend.com) and from Keil Software (www.keil.com/support).

#### Using the Keil µVision2 IDE

$\mu$ Vision2 is an IDE that brings together all aspects of your embedded application.

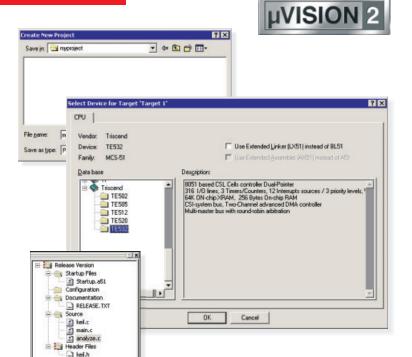

#### **Starting a Project**

When creating a new project in  $\mu$ Vision2, you must first select the folder and filename.  $\mu$ Vision2 then prompts you to select the device you will use. The Keil development tools for the 805 I support all 805 I variants including the Triscend E5 Devices.

#### **Organizing Project Settings**

$\mu$ Vision2 projects are composed of one or more targets, groups, and files.

Targets define the chip to use as well as all assembler, compiler, linker, and debugger settings for an executable. A project may have more than one target. For example, you can have a target for debugging and another target for your release software.

Groups provide you with a way to separate and organize the source files in a project. When adding files to the project, you may add all files to a single group or you may create groups for startup code, documents, source, and header files.

FastChip generates C header and source files you may include in your  $\mu$ Vision2 project to initialize the on-chip peripherals of your Triscend device.

#### **Setting Tool Options**

Most tool options are automatically set when you select the device you use. Other options like memory size, folder names, source browser settings, and output controls may be configured from the Project Options Dialog.

#### **Building Your Application**

After adding files and setting options,  $\mu$ Vision2 allows you to interactively build and correct syntax errors in your project. Double-click on an error to edit the corresponding line in your program source.

#### Using the Keil µVision2 Debugger

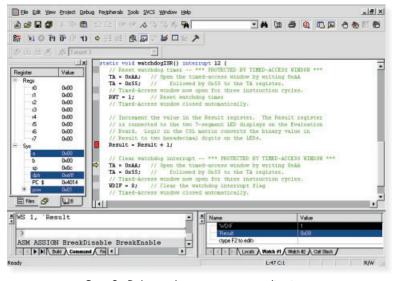

#### **Debugging E5 Programs**

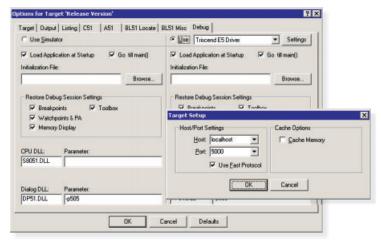

The  $\mu$ Vision2 Debugger and the Triscend E5 Debugger Driver allow you to test your embedded CSoC applications running on target hardware. When you use the E5 Driver, your target program is downloaded to your target system using the on-chip JTAG interface.

You must select the Triscend Driver as your debugger interface when you configure the debugger. Typically, all driver options are set automatically.

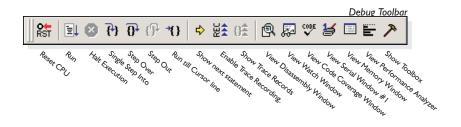

#### **Executing Code**

You may use the buttons on the debug toolbar to step through your application program. The **Run** button executes code until a breakpoint is reached while the **Halt Execution** button stops program execution immediately. **Single Step Into** executes one line of assembly or C source code stepping into a functions.

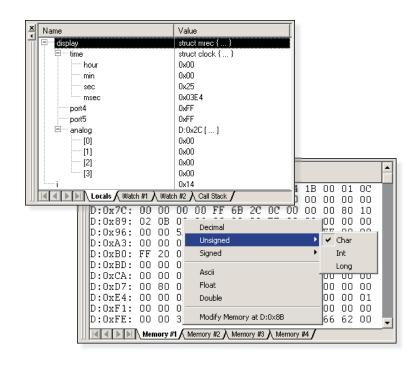

#### Watching Variables

The  $\mu$ Vision2 Debugger allows you to watch the local variables of each C function. Two user-defined watch windows allow you to specify and watch special program variables. Viewing complex structures, unions, and arrays is supported. Elements may be expanded or collapsed as necessary. Simply select a variable to change its value while debugging.

#### **Viewing Memory**

Four memory windows allow you to watch different memory areas used by your program code. You may watch a fixed address or enter a symbol name in the Watch Window Address box.

#### **More Details**

The  $\mu$ Vision2 Debugger offers features typically available only in high-end emulators. For more information, visit **www.keil.com/uvision2**.

Configure the Debugger in the Project Options Dialog.

#### Devices Available from Triscend

| Part<br>Number | User<br>I/O | Timers<br>Counters | Interrupt<br>Sources | Watchdog<br>Timer | On-chip<br>XRAM | DMA<br>Controller | CSL<br>Cells | Packages        |

|----------------|-------------|--------------------|----------------------|-------------------|-----------------|-------------------|--------------|-----------------|

| TE502          | 92          | 3                  | 12                   | 1                 | 8K              | 1                 | 256          | 128LQFP         |

| TE505          | 124         | 3                  | 12                   | ✓                 | 16K             | ✓                 | 512          | 128LQFP. 208QFP |

| TE512          | 188         | 3                  | 12                   | 1                 | 32K             | 1                 | 1152         | 128LQFP, 208QFP |

| TE520          | 252         | 3                  | 12                   | ✓                 | 40K             | ✓                 | 2048         | 208QFP, 484BGA  |

#### **Triscend E5 Family Highlights**

- Performance accelerated 8051 microcontroller core (10 MIPS at 40 MHz)

- Binary and source code compatible with other 8051 variants

- Stand-alone operation from a single external memory (code + configuration)

- Up to 40 KBytes of on-chip, dedicated system RAM

- Up to 2048 Configurable System Logic (CSL) cells (up to 25,000 **ASIC** gates)

- Power-down and power-management modes (low power mode consumption under 100  $\mu$ A)

- Compliant to the CSI Socket interface, allowing soft peripherals to be used on other CSoC Families

- Two dedicated DMA Channels

- On-chip breakpoint unit provides sophisticated debugging capability

- |TAG debugging using the Keil μVision2 Debugger

1501 10th Street, Suite 110 Plano, TX 75074

Phone 800-348-8051 972-312-1107 FAX 972-312-1159 PRSRT STD U.S. Postage PAID Dallas, TX Permit #4910