# 51MX Architecture Reference Specification and Instruction Set

Preliminary July 19, 2002

Version 0.9

| 1  | Intro       | duction to The 51MX Architecture                                                       | 1  |

|----|-------------|----------------------------------------------------------------------------------------|----|

|    | 1.1         | Key 51MX architecture enhancements                                                     |    |

|    | 1.2         | Compatibility Considerations with the 80C51                                            |    |

| •  | More        | owy Ovacovination                                                                      | 1  |

| 2  | 2.1         | ory Organization                                                                       |    |

|    | 2.1         | 51MX Versus 80C51 Programmer's Models and Memory Maps                                  |    |

|    | 2.2         | Data Memory (DATA, IDATA, and EDATA)                                                   |    |

|    |             | 2.2.1 Registers R0 - R7                                                                |    |

|    |             | <ul><li>2.2.2 Bit Addressable RAM</li><li>2.2.3 Extended Data Memory (EDATA)</li></ul> |    |

|    |             |                                                                                        |    |

|    |             | 2.2.4 Stack                                                                            |    |

|    | 2.2         | 2.2.5 General Purpose RAM                                                              |    |

|    | 2.3         | Special Function Registers (SFRs)                                                      |    |

|    | 2.4         | External Data Memory (XDATA)                                                           |    |

|    | 2.5         | High Data Memory (HDATA)                                                               |    |

|    | 2.6         | Program Memory (CODE)                                                                  |    |

|    | 2.7         | Universal Pointers                                                                     | 14 |

| 3  | Instr       | uction Set Overview                                                                    | 19 |

|    |             |                                                                                        |    |

| 4  |             | rupt Processing                                                                        |    |

|    | 4.1         | Interrupt Enables AND Priorities                                                       | 21 |

| 5  | Exte        | rnal Bus                                                                               | 22 |

|    | 5.1         | Multiplexed External Bus                                                               |    |

|    |             | •                                                                                      |    |

| Ap | pendix      |                                                                                        |    |

|    | <b>A.</b> 1 | Glossary of terms and notation used in this section                                    |    |

|    | A.2         | 51MX Instruction Set Summary                                                           |    |

|    |             | Detailed Instruction Descriptions                                                      | 32 |

|    |             | ACALL Absolute Call                                                                    | 32 |

|    |             | ADD Add Byte                                                                           | 33 |

|    |             | ADD Add to Universal Pointer .(extended instruction)                                   | 34 |

|    |             | ADDC Add with Carry                                                                    | 35 |

|    |             | AJMP Absolute Jump                                                                     | 36 |

|    |             | ANL Logical AND Byte                                                                   | 37 |

|    |             | ANL Logical AND Bit                                                                    | 39 |

|    |             | CJNE Compare and Jump if Not Equal                                                     | 40 |

|    |             | CLR Clear Accumulator                                                                  | 42 |

|    |             | CLR Clear Bit                                                                          | 43 |

|    |             | CPL Complement Accumulator                                                             | 44 |

|    |             | CPL Complement Bit                                                                     |    |

|    |             | DA Decimal Adjust Accumulator                                                          |    |

|    |             | DEC Decrement                                                                          |    |

|    |             | DIV Divide                                                                             |    |

| DJNZ        | Decrement and Jump if Not Zero                           | 49 |

|-------------|----------------------------------------------------------|----|

| ECALL       | Extended Call(extended instruction)                      | 50 |

| EJMP        | Extended Jump(extended instruction)                      | 51 |

| EMOV        | Move Data Using Universal Pointer (extended instruction) | 52 |

| ERET        | Extended Return from Subroutine (extended instruction)   | 53 |

|             | Increment                                                |    |

| INC         | Increment Data Pointer                                   | 55 |

| INC         | Increment Extended Pointer(extended instruction)         | 56 |

| JB          | Jump if Bit Set                                          | 57 |

| JBC         | Jump if Bit is Set and Clear Bit                         | 58 |

|             | Jump if Carry is Set                                     |    |

| JMP         | Jump Indirect using DPTR                                 | 60 |

| JMP         | Jump Indirect using EPTR(extended instruction)           | 61 |

| JNB         | Jump if Bit is Not Set                                   | 62 |

| JNC         | Jump if Carry Not Set                                    | 63 |

| JNZ         | Jump if Accumulator is Not Zero                          | 64 |

| JZ          | Jump if Accumulator is Zero                              | 65 |

| LCALL       | Long Call                                                | 66 |

| LJMP        | Long Jump                                                | 67 |

| MOV         | Move Byte                                                | 68 |

| MOV         | Move Bit                                                 | 71 |

| MOV         | Move Value to Data Pointer                               | 72 |

| MOV         | Move Value to Extended Pointer(extended instruction)     | 73 |

| MOVC        | Move Code Byte(extended instruction)                     | 74 |

| MOVX        | Move External Data Byte (extended instruction)           | 76 |

| $MUL \dots$ | Multiply                                                 | 78 |

| NOP         | No Operation                                             | 79 |

| ORL         | Logical OR Byte                                          | 80 |

| ORL         | Logical OR Bit                                           | 82 |

| POP         | Pop Data from Stack                                      | 83 |

|             | Push Data onto Stack                                     |    |

|             | Return from Subroutine(extended instruction)             |    |

| RETI        | Return from Interrupt(extended instruction)              | 86 |

| RL          | Rotate Left                                              | 87 |

| RLC         | Rotate Left through Carry Flag                           | 88 |

|             | Rotate Right                                             |    |

| RRC         | Rotate Right through Carry Flag                          | 90 |

|             | Set Bit                                                  |    |

|             | Short Jump                                               |    |

|             | Subtract with Borrow                                     |    |

| SWAP        | Swap Nibbles in Accumulator                              | 95 |

| XCH         | Exchange Byte                                            | 96 |

| XCHD        | Exchange Digit                                           | 97 |

| XRI.        | Logical Exclusive-Or Byte                                | 98 |

# 1 INTRODUCTION TO THE 51MX ARCHITECTURE

The 51MX is a true binary-level superset of the classic 80C51 architecture, transparently adding access to both code and data memory beyond the original 64 kilobyte (KB) limit, up to the maximum of 8 megabytes (MB) of code and 8 MB minus 64 KB of data, in a non-segmented linear space. The 51MX is completely backward compatible with the 80C51. Code written for the 80C51 may be run on the 51MX with no changes.

# 1.1 KEY 51MX ARCHITECTURE ENHANCEMENTS

The 51MX architecture provides a seamless and compelling upgrade path from the classic 80C51 by offering easy memory extension combined with enhanced high level language performance and efficiency.

- Program Counter: The Program Counter is extended to 23 bits. Code size up to 8 MB is accessed in linear, non-segmented

approach, eliminating inefficient bank-switching solutions when crossing 64 KB boundary.

- Extended Data Pointer: A 23-bit Extended Data Pointer EPTR is added in order to allow simple extension to existing assembly

language programs that must be expanded to address more than 64 KB of data memory.

- Stack: Two independent alternate Stack modes are added. The first causes addresses pushed onto the Stack by interrupts to be expanded to 23 bits. The second allows Stack extension into a larger memory space.

- Instruction set: A small number of instructions now have extended addressing modes to allow full use of extended code and data addressing.

- Addressing Modes: A new addressing mode, Universal Pointer mode, is added so that any area of code and data can be

accessed with a single instruction. Using this feature, high level languages compilers, such as C, can easily produce more

efficient code, both in terms of size and execution time.

- Extended SFR space: additional 128 bytes of Special Function Register addressing allows easy access to the broad range of advanced 51MX peripherals.

# 1.2 COMPATIBILITY CONSIDERATIONS WITH THE 80C51

An equally important objective for the 51MX is to retain complete compatibility with the familiar classic 80C51. The 80C51 is the most widely used 8-bit microcontroller architecture in the world and as a result, a vast amounts of code have been written. Therefore preservation of customer's investment in code and hardware development is a critical consideration.

- Instruction set: The 51MX implements the entire 80C51 instruction set with identical instruction encoding.

- CPU: The 51MX adds a small number of register and instruction extensions needed for extended addressing.

- Timing: The 51MX has standard 6-clock 80C51 machine cycle timing. If the 51MX replaces an older 80C51 device using 12-clock machine cycles, it will run exactly twice as fast as the original device.

- Memory Map: A major consideration in hardware compatibility of the 51MX with the 80C51 is the memory map. The 51MX implements the entire 80C51 memory map, adding to it in a transparent manner where necessary to extend the address space to 8 MB each of code and data.

- Stack operation: The 51MX duplicates 80C51 stack operations precisely as its default configuration. The 51MX can be

configured to extend the stack by increasing the Stack Pointer to 16-bits and allowing it to access the Extended Data

memory. When the program size expands beyond 64 KB, the extended interrupt frame mode saves and restores the full

23-bit Program Counter.

- SFR Access: Where 51MX devices implement the same feature set as an earlier 80C51 device, SFR addresses will remain

unchanged such that code from the original device will run with no changes. If the 51MX device has additional features,

it may not always be possible to use the same SFR addresses for all features.

- Pin-for-pin compatibility. 51MX derivatives are generally intended to be pin-compatible with 80C51 derivatives that have the same feature set. When extended addressing is enabled, additional address lines may replace some port functions.

- Bus Interface: The 51MX external bus operates in the same manner as a classic 80C51. Extended addressing does not take effect unless it is enabled by configuration or by software, so the additional address lines remain inactive unless needed, allowing the pins to be used for other purposes, such as general purpose I/O.

# 2 MEMORY ORGANIZATION

# 2.1 51MX VERSUS 80C51 PROGRAMMER'S MODELS AND MEMORY MAPS

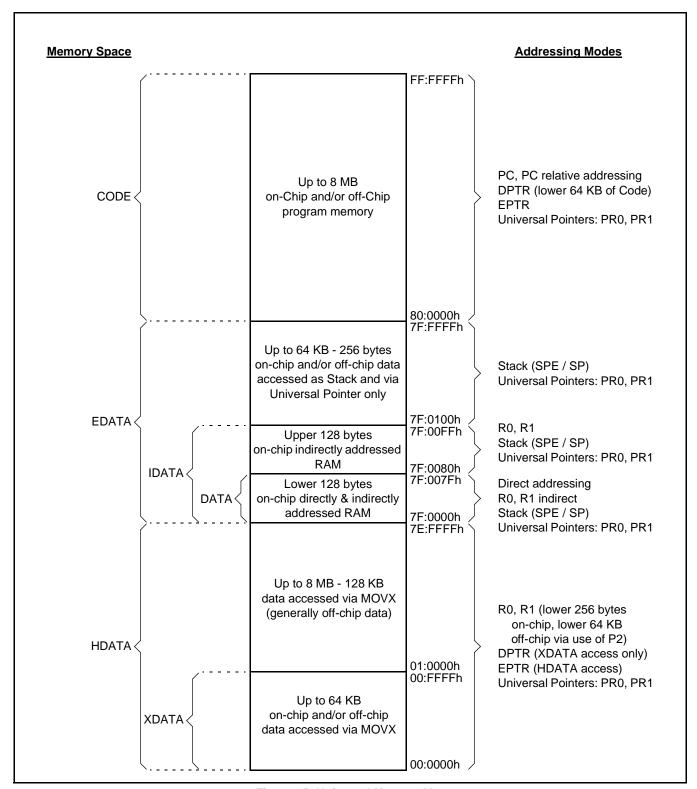

The 51MX retains all of the 80C51 memory spaces. Additional memory space has been added transparently as part of the means for allowing extended addressing. The basic memory spaces include code memory (which may be on-chip, off-chip, or both); external data memory (a portion of which is always on-chip); Special Function Registers; and internal data memory, which includes on-chip RAM, registers, and stack. Provision is made for internal data memory to be extended, allowing a larger processor stack.

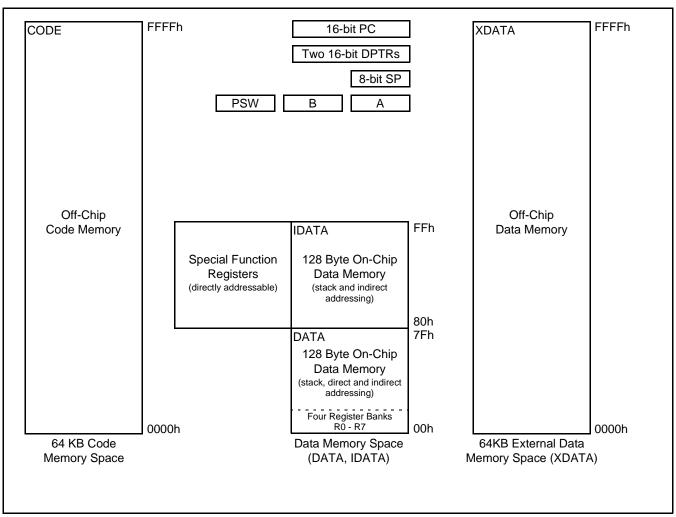

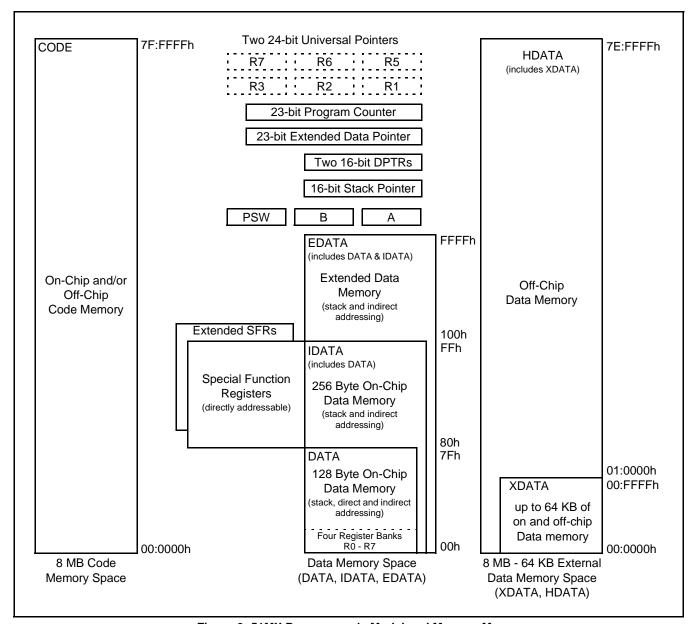

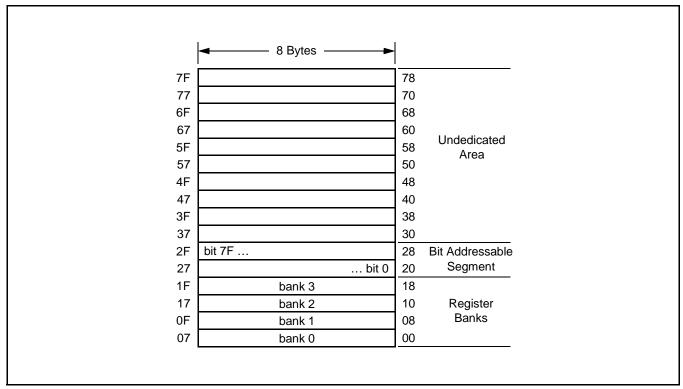

The classic 80C51 programmer's model and memory map is shown in Figure 1 for reference. The 51MX programmer's model and memory map is shown in Figure 2.

Figure 1: Classic 80C51 Architecture Programmer's Model and Memory Map

Figure 2: 51MX Programmer's Model and Memory Map

Detailed descriptions of each of the various 51MX memory spaces may be found following this summary.

DATA 128 bytes of internal data memory space (00h...7Fh) accessed via direct or indirect addressing, using instructions other than MOVX and MOVC. All or part of the Stack may be in this area.

IDATA Indirect Data. 256 bytes of internal data memory space (00h...FFh) accessed via indirect addressing using instructions other than MOVX and MOVC. All or part of the Stack may be in this area. This area includes the DATA area and the 128 bytes immediately above it.

51MX

| EDATA | Extended Data. This space is a superset of DATA and IDATA areas and allows up to a potential total of 64 KB       |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | (including those areas). The added area may be accessed only as Stack and via indirect addressing using Universal |

|       | Pointers. Part of this space is always implemented on-chip.                                                       |

- SFR Special Function Registers. Selected CPU registers and peripheral control and status registers, accessible only via direct addressing (addresses in range 80h...FFh). This includes the new 51MX extended SFRs.

- XDATA "External" Data. Duplicates the classic 80C51 64 KB memory space addressed via the MOVX instruction using the DPTR, R0, or R1. Part of this space is implemented on-chip. On-chip XDATA can be disabled under program control. Also, XDATA may be placed in external devices.

- HDATA "High" Data. This is a superset of XDATA and may include up to 8,323,072 bytes (8 MB 64 KB) of memory space addressed via the MOVX instruction using the EPTR, DPTR, R0, or R1. Non XDATA portion of HDATA is placed in external devices.

- CODE Up to 8 MB of Code memory, accessed as part of program execution and via the MOVC instruction.

All of these spaces except the SFR space may also be accessed through use of Universal Pointer addressing with the EMOV instruction. This feature is detailed in a subsequent section.

# 2.2 DATA MEMORY (DATA, IDATA, AND EDATA)

The standard 80C51 internal data memory consists of 256 bytes of DATA/IDATA RAM, and is always entirely on-chip. In this space are the data registers R0 through R7, the default stack, a bit addressable RAM area, and general purpose data RAM. On the top of the DATA/IDATA memory space is the rest of Extended Data Memory (EDATA) that provides up to a possible 64 KB of total EDATA memory. Stack by default resides in DATA/IDATA space, but may be configured to extend into the rest of EDATA. The different portions of the data memory are accessed in different manners as described in the following sections.

#### 2.2.1 **REGISTERS R0 - R7**

General purpose registers R0 through R7 allow quick, efficient access to a small number of internal data memory locations. For example, the instruction:

MOV A,R0

uses one byte of code and executes in one machine cycle. Using direct addressing to accomplish the same result as in:

MOV A,10h

requires two bytes of code memory and executes in two machine cycles. Indirect addressing further requires setup of the pointer register, etc.

These registers are "banked". There are four groups of registers, any one of which may be selected to represent R0 through R7 at any particular time. This feature may be used to minimize the time required for context switching during an interrupt service or a subroutine, or to provide more register space for complicated algorithms.

The registers are no different from other internal data memory locations except that they can be addressed in "shorthand" notation as "R0", "R1", etc. Instructions addressing the internal data memory by other means, such as direct or indirect addressing, are quite capable of accessing the same physical locations as the registers in any of the four banks.

## 2.2.2 BIT ADDRESSABLE RAM

Internal data memory locations 20h through 2Fh may be accessed as both bytes and bits. This allows a convenient and efficient way to manipulate individual flag bits without using much memory space. The bottom bit of the byte at address 20h is bit number 00h, the next bit in the same byte is bit number 01h, etc. The final bit, bit 7 of the byte at address 2Fh, is bit number 7Fh (127 decimal). Bit numbers above this refer to bits in Special Function Registers.

This code:

SETB 20h.1 CPL 20h.2

JNB 20h.2, LABEL1

sets bit 1 at address 20h, complements bit 2 in the same byte, then branches if the second bit is not equal to 1. In an actual program, these bits would normally be given names and referred to by those names in the bit manipulation instructions.

# 2.2.3 EXTENDED DATA MEMORY (EDATA)

The 51MX architecture allows for extension of the internal data memory space beyond the traditional 256 byte limit of classic 80C51s. This space can be used as an extended or alternative processor stack space, or can be used as general purpose storage under program control. Other than Stack Pointer based access to this space, which is automatic if Extended Stack Memory Mode is enabled (ESMM=1 in MXCON sfr; see the following Stack section), this memory is addressed only using the new Universal Pointer feature. Universal Pointers are described in a later section.

### 2.2.4 STACK

The processor stack provides a means to store interrupt and subroutine return addresses, as well as temporary data. The stack grows upwards, from lower addresses towards higher addresses. The current Stack Pointer always points to the last item pushed on the stack, unless the stack is empty. Prior to a push operation, the Stack Pointer is incremented, then data is written to memory. When the stack is popped, the reverse procedure is used. First, data is read from memory, then the Stack Pointer is decremented.

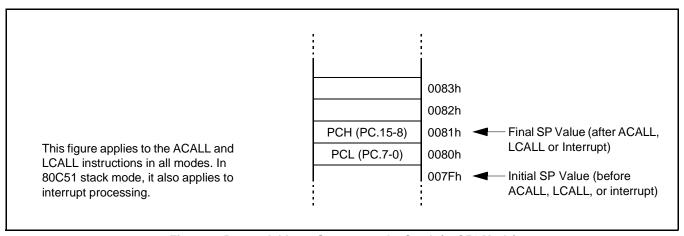

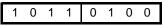

The default configuration of the 51MX stack is identical to the classic 80C51 stack implementation. When interrupt or subroutine addresses are pushed onto the stack, only the lower 16 bits of the Program Counter are stored. This default 80C51 mode stack operation is shown in Figure 3.

Figure 3: Return Address Storage on the Stack (80C51 Mode)

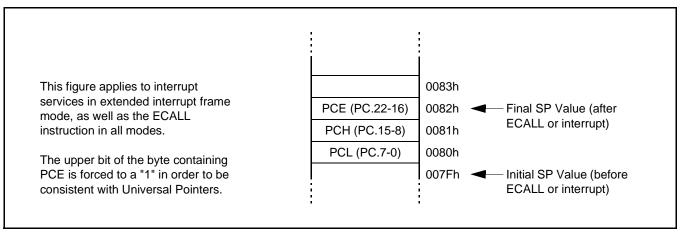

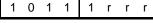

There are two configuration options for the stack. For purposes of backward compatibility with the classic 80C51, both alternate modes are disabled by a chip reset. The first option, Extended Interrupt Frame Mode, causes interrupts to push the entire 23-bit

Program Counter onto the stack (as three bytes), and the RETI instruction to pop all 23-bits as a return address, as shown in Figure 4. The upper bit of the stack byte containing the most significant byte of the Program Counter is forced to a "1" to be consistent with Universal Pointer addressing.

Storing the full 23-bit Program Counter value is a requirement for systems that include more than 64 KB of program, since an interrupt could occur at any point in the program. The Extended Interrupt Frame Mode changes the operation of interrupts and the RETI instruction only, other calls and returns are not affected. Special extended call and return instructions allow large programs to traverse the entire code space with full 23-bit return addresses. The Extended Interrupt Frame Mode is enabled by setting the EIFM bit in the MXCON register.

Figure 4: Extended Return Address Storage on the Stack

The second stack option, Extended Stack Memory Mode, allows for stack extension beyond the 256 byte limit of the classic 80C51 family. Stack extension is accomplished by increasing the Stack Pointer to 16 bits in size and allowing it to address the entire EDATA memory rather than just the standard 256 byte internal data memory. Stack extension has no effect on the data that is stored on the stack, it will continue to be stored as shown on in Figure 3 and Figure 4. The Extended Stack Memory Mode is enabled by setting the ESMM bit in the MXCON register.

If the Stack Pointer is not initialized by software, the stack will begin at on-chip RAM address 8, just as for the 80C51. Also note that in Extended Stack Memory Mode, the size of the EDATA space (and therefore its ending address) may not be the same for all 51MX systems, it will depend on the size of the EDATA RAM physically implemented for a specific 51MX derivative.

The stack mode bits ESMM and EIFM are shown in Figure 5. Note that the stack mode bits are intended to be set once during program initialization and not altered after that point. Changing stack modes dynamically may cause stack synchronization problems.

| Not bit address: | able   | 7                                                                                                                                | 6                                                                             | 5                                                                                                | 4                                                                                 | 3                                                                 | 2                                                                    | 1                                                                                            | 0                                                                                         |  |

|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Reset Value: 00  | )h     | -                                                                                                                                | -                                                                             | -                                                                                                | -                                                                                 | -                                                                 | EAM                                                                  | ESMM                                                                                         | EIFM                                                                                      |  |

| BIT              | SYMBOL | FUNCTION                                                                                                                         |                                                                               |                                                                                                  |                                                                                   |                                                                   |                                                                      |                                                                                              |                                                                                           |  |

| MXCON.7 - 3      | -      | Reserved. Pr                                                                                                                     | rograms s                                                                     | should not                                                                                       | write a 1 to                                                                      | these bit                                                         | s.                                                                   |                                                                                              |                                                                                           |  |

| MXCON.2          | EAM    | Enables Extended bit. The logical code and data read from this 64 KB each of beyond bound multiplexed consection for acceptance. | al OR of the anadress bit by so of code are dary of 6 on Port 2 diditional of | ne SFR bit a<br>sing beyon<br>oftware. W<br>nd data. W<br>4 KB to 8 N<br>for externa<br>details. | and the no<br>ld 64 KB is<br>hen 0, all a<br>hen 1, 51<br>MB each o<br>I code and | n-volatile of allowed. addressing MX addres f code and dor data a | configuration The same go (on-chip assing capal dota, and ccesses. F | on bit detern<br>logical OR<br>and off-chip<br>bilities are of<br>lupper add<br>Refer to the | mines wheth<br>value will b<br>o) is limited<br>extended<br>lress bits are<br>External Bo |  |

|                  |        | EAM must be set to EAM=1 if at least one of the next two statements is true:                                                     |                                                                               |                                                                                                  |                                                                                   |                                                                   |                                                                      |                                                                                              |                                                                                           |  |

|                  |        | - there is executable code or constants in CODE space are above 64 KB                                                            |                                                                               |                                                                                                  |                                                                                   |                                                                   |                                                                      |                                                                                              |                                                                                           |  |

|                  |        | - address of data byte that has to be accessed in HDATA is above 64 KB                                                           |                                                                               |                                                                                                  |                                                                                   |                                                                   |                                                                      |                                                                                              |                                                                                           |  |

| MXCON.1          | ESMM   | Enables the I<br>in width and t<br>Pointer is inc<br>EDATA space                                                                 | he stack i<br>reased to                                                       | s located in 16-bits in                                                                          | n the IDAT<br>width and                                                           | A memory<br>the stack                                             | space. Will<br>may be loo                                            | hen ESMM                                                                                     | = 1, the Sta                                                                              |  |

| MXCON.0          | EIFM   | Enables the cause only the will restore or all 23 bits of 23 bits of the first 64 KB of                                          | e lower 1<br>hly the low<br>the PC to<br>PC. EIFM                             | 6 bits of the<br>ver 16 bits of<br>be pushed<br>If <u>must</u> be                                | e PC to be<br>of the PC.<br>d onto the                                            | pushed or<br>When EIFI<br>stack, whi                              | nto the stac<br>M = 1, an ir<br>le a RETI i                          | ck, and a Ri<br>nterrupt ser<br>instruction                                                  | ETI instructi<br>vice will cau<br>will restore                                            |  |

Figure 5: 51MX Configuration Register (MXCON)

## 2.2.5 GENERAL PURPOSE RAM

Portions of the internal data memory that are not used in a particular application as registers, stack, or bit addressable locations may be considered general purpose RAM and used in any desired manner.

The lower 128 bytes of the internal data memory (DATA) may be accessed using either direct or indirect addressing. Direct addressing incorporates the entire address within the instruction. For example, the instruction:

MOV 31h,#10

will store the value 10 (decimal) in location 31h. Direct addresses above 128 will access the Special Function Registers rather than the internal data memory.

Indirect addressing takes an address from either R0 or R1 of the current register bank and uses it to identify a location in the internal data memory. The entire 256 byte internal data memory space (IDATA) may be accessed using indirect addressing. For example, the instruction sequence:

51MX

MOV R0,#90h MOV A,@R0

will cause the contents of location 90 hex to be loaded into the accumulator. It is typical with the classic 80C51 to cause the stack to be located in the upper area, leaving more general purpose RAM in the lower area that may be accessed using both direct and indirect addressing. With the 51MX, the stack may be extended and moved completely out of the lower 256 bytes of memory.

Figure 6: Internal Data Memory, Lower 128 Bytes

# 2.3 SPECIAL FUNCTION REGISTERS (SFRS)

Special Function Registers (SFRs) provide a means for the processor to access internal control registers, peripheral devices, and I/O ports. An SFR address is always contained entirely within an instruction.

The standard SFR space is 128 bytes in size. SFRs are implemented in each 51MX device as needed in order to provide control for peripherals or access to CPU features and functions. Each 51MX derivative may have a different number of SFRs implemented because each has a different set of peripheral functions. Many SFR addresses will typically be unused on any particular derivative. Those undefined SFRs are considered "reserved" and should not be accessed by user programs. However, if these bits are accessed, they should be filled with "0"s, in order to maintain the code compatibility with future parts.

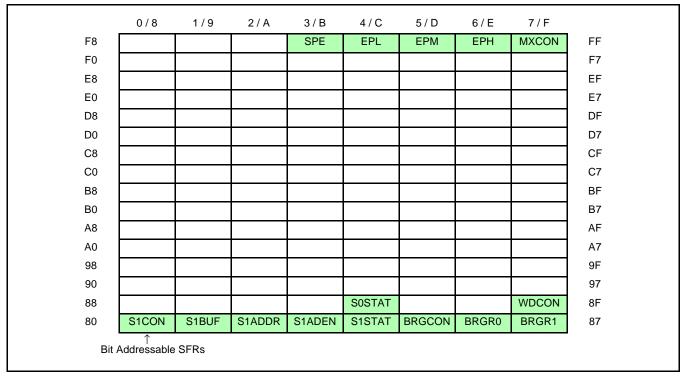

Sixteen addresses in the SFR space are both byte- and bit-addressable. The bit-addressable SFRs are those whose address ends in 0h or 8h (i.e. 80h, 88h, ..., F8h). Bit addressing allows direct control and testing of bits in those SFRs. Figure 7 shows the SFR map for the first 51MX devices, the 87MC51Mx2 family (87C51MB2, and 87C51MC2).

|       | 0/8                | 1/9    | 2 / A  | 3/B    | 4/C    | 5/D    | 6/E    | 7 / F |    |

|-------|--------------------|--------|--------|--------|--------|--------|--------|-------|----|

| F8    | IP1                | CH     | CCAP0H | CCAP1H | CCAP2H | ССАРЗН | CCAP4H |       | FF |

| F0    | В                  |        |        |        |        |        |        | IP1H  | F7 |

| E8    | IEN1               | CL     | CCAP0L | CCAP1L | CCAP2L | CCAP3L | CCAP4L |       | EF |

| E0    | ACC                |        |        |        |        |        |        |       | E7 |

| D8    | CCON               | CMOD   | CCAPM0 | CCAPM1 | CCAPM2 | ССАРМ3 | CCAPM4 |       | DF |

| D0    | PSW                |        |        |        |        |        |        |       | D7 |

| C8    | T2CON              | T2MOD  | R2CAPL | R2CAPH | TL2    | TH2    |        |       | CF |

| C0    |                    |        |        |        |        |        |        |       | C7 |

| B8    | IP0                | S0ADEN |        |        |        |        |        |       | BF |

| B0    | P3                 |        |        |        |        |        |        | IP0H  | В7 |

| A8    | IEN0               | S0ADDR |        |        |        |        |        |       | AF |

| A0    | P2                 |        | AUXR1  |        |        |        | WDRST  |       | A7 |

| 98    | SOCON              | S0BUF  |        |        |        |        |        |       | 9F |

| 90    | P1                 |        |        |        |        |        |        |       | 97 |

| 88    | TCON               | TMOD   | TL0    | TL1    | TH0    | TH1    | AUXR   |       | 8F |

| 80    | P0                 | SP     | DPL    | DPH    |        |        |        | PCON  | 87 |

| Bit A | ↑<br>ddressable \$ | SFRs   |        |        |        |        |        |       |    |

Figure 7: Standard SFR Map for the 87C51Mx2

SFR addresses tend to be in very short supply in more complex 80C51 derivatives, especially in the case of bit addressable SFRs. Therefore, a method to extend the SFR space is implemented on the 51MX. When any instruction that references an SFR (including a bit address in an SFR) is preceded by the escape opcode A5h, an alternate bank of SFRs (extended SFRs) will be accessed. Thus, extended SFRs take one machine cycle longer to access and use one additional byte of memory to encode than standard SFRs.

Due to the method by which extended SFRs are accessed, each 51MX instruction may access only standard SFRs or extended SFRs with explicit addressing. This is only an issue for the instruction "MOV direct, direct". When used to access two SFRs, the 51MX restricts this instruction to access only SFRs in the same space (standard SFR space or extended SFR space). Note that instructions such as "MOV A, direct" refer to the Accumulator *implicitly* (the address of the Accumulator is not encoded in the instruction) and can therefore be used with either SFR bank. The complete list of instructions that may access a byte or bit in both a standard and extended SFR (by addressing one implicitly and one explicitly) follows:

9

```

ADD

A, direct

ADDC

A, direct

A,direct

SUBB

ANL

A, direct

ANL

direct,A

ORL

A, direct

direct,A

ORL

XRL

A, direct

direct,A

XRL

MOV

A, direct

MOV

direct,A

XCH

A, direct

C,bit

ANL

ANL

C,/bit

ORL

C,bit

ORL

C,/bit

```

51MX

MOV C,bit

MOV bit,C

CJNE A,direct,rel

Several SFRs have been defined that will be present on any 51MX derivative. These are: MXCON, EPH, EPM, EPL, and SPE. MXCON contains the bits that control 51MX specific functions, including the Stack Mode control bits and the External Bus Mode control bit. EPH, EPM, and EPL comprise the EPTR. SPE contains the upper byte of the Stack Pointer when the stack is in Extended Stack Memory Mode. All of these SFRs are located in the extended SFR bank. Figure 8 shows the extended SFR map for the 87C51Mx2.

Figure 8: Extended SFRs Map for the 87C51Mx2 (First 51MX Derivative)

# 2.4 EXTERNAL DATA MEMORY (XDATA)

The XDATA space on the 51MX is the same as the 64 KB external data memory space on the classic 80C51.

On-chip XDATA memory can be disabled under program control via the EXTRAM bit in the AUXR register. Accesses above implemented on-chip XDATA will be routed to the external bus. If on-chip XDATA memory is disabled, all XDATA accesses will be routed to the external bus.

# 2.5 HIGH DATA MEMORY (HDATA)

The 51MX architecture supports up to an 8 MB data memory space, using 23-bit addressing. The entire 8 MB space except for the 64 KB EDATA space is called HDATA. The XDATA space comprises the lower 64 KB of HDATA.

10

#### **Data Pointers**

The 51MX adds an additional 23-bit Extended Data Pointer (EPTR) in order to allow a simple method of extending existing 80C51 programs to use more than 64 KB of data memory. To access a single data byte from HDATA RAM located above the first 64 KB, the EAM bit in MXCON must be set to EAM=1.

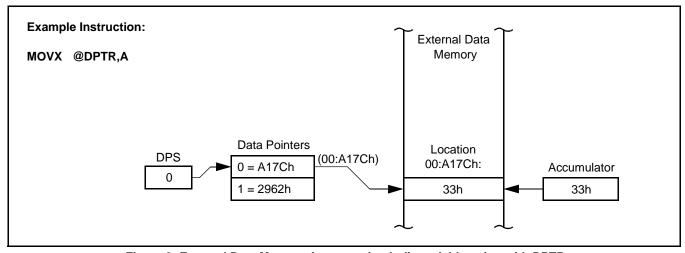

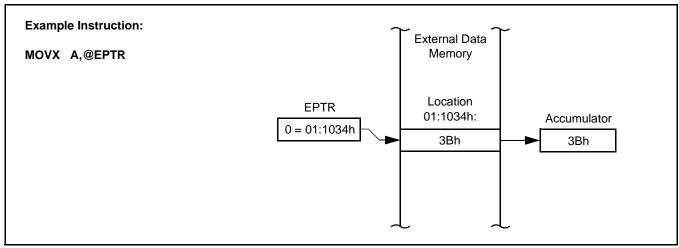

All 80C51 instructions that use the DPTR have an 51MX variant that uses the EPTR. The 23-bit EPTR is comprised of (in order) EPH, EPM, and EPL. Figures 9 and 10 show examples of indirect accesses to data memory using the DPTR and the EPTR respectively. Since the EPTR is a 23-bit value, the 8th bit of EPH is not used. If read, it will return a 1. Use of the EPTR allows access to the entire HDATA space, including XDATA.

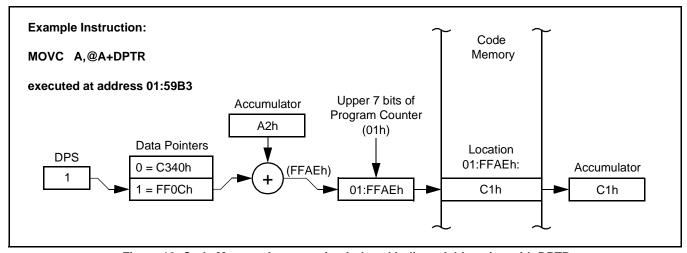

At any point in time, one specific Data Pointer is active and used by instructions that reference the DPTR. The active DPTR may be changed by altering the Data Pointer Select (DPS) bit. The DPS bit occupies the bottom bit of the AUXR1 register. The DPS bit applies only to the two DPTRs, not to the EPTR.

In the indirect addressing mode, the currently active DPTR or the EPTR provides a data memory address for accessing the XDATA and HDATA space respectively. When the DPTR is used for addressing, only the XDATA space is available. When the EPTR is used for addressing, the entire HDATA space (which includes the XDATA space) may be accessed. If the EPTR value exceeds 7E:FFFF (the limit of HDATA), data accesses using EPTR will yield undefined results. The reason for limiting HDATA addresses is to keep the addressing uniform for EPTR addressing and Universal Pointer addressing (which is explained in a later section of this document).

Figure 9: External Data Memory Access using Indirect Addressing with DPTR

Figure 10: External Data Memory Access using Indirect Addressing with EPTR

# 2.6 PROGRAM MEMORY (CODE)

The 80C51, and thus the 51MX, are "Harvard" architectures, meaning that the code and data spaces are separated. If there is any portion of executable code above 64 KB that can be interrupted, EAM bit in MXCON must be set to EAM=1. Also, if there is even the slightest amount of constants used by the application and placed in CODE space above 64 KB boundary, EAM must be set to EAM=1.

The 51MX expands the 80C51 Program Counter to 23 bits, providing a continuous, unsegmented linear code space that may be as large as 8 MB. On-chip space begins at code address 0 and extends to the limit of the on-chip code memory. Above that, code will be fetched from external. The 51MX architecture allows for an external bus which supports:

- Mixed mode (some code and/or data memory off-chip).

- Single-chip operation (no external bus connection).

- · ROMless operation (no use of on-chip code memory).

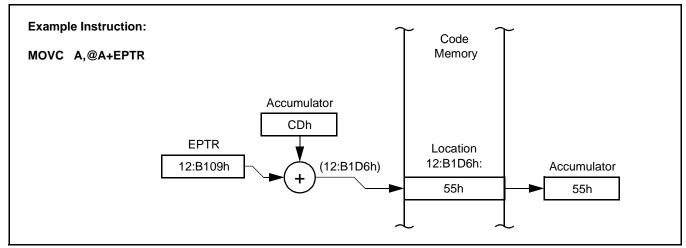

In some cases, code memory may be addressed as data. Extended instruction address modes provide access to the entire code space of 8 MB through the use of indexed indirect addressing. The currently active DPTR, the EPTR, a Universal Pointer, or the Program Counter may be used as the base address. Examples of the various code memory addressing modes are shown in figures 11 through 13.

Following a reset, the 51MX begins code execution like a classic 80C51, at address 00:0000h. Similarly, the interrupt vectors are placed just above the reset address, starting at address 00:0003h. It is important to note that the first instruction (located at address 0) must not be an EJMP instruction. EJMP is a 5 byte instruction and would overlap any instructions intended for the external interrupt 0 vector address.

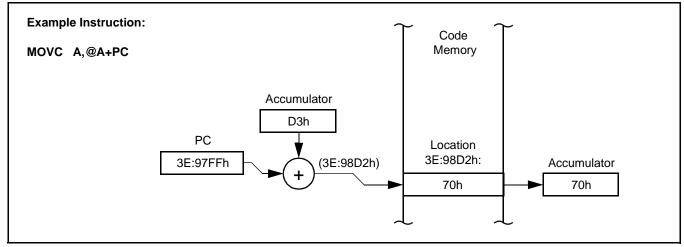

Figure 11: Code Memory Access using Indexed Indirect Addressing with the Program Counter

Figure 12: Code Memory Access using Indexed Indirect Addressing with DPTR

Figure 13: Code Memory Access using Indexed Indirect Addressing with EPTR

# 2.7 UNIVERSAL POINTERS

A new addressing mode called Universal Pointer mode has been added to the 51MX, specifically for the purpose of greatly enhancing C language code density and performance. This addressing mode allows access to any of the on-chip or off-chip code and data spaces using one instruction, without the need to know in advance which of the different spaces the data will reside in. This includes the DATA, IDATA, EDATA, XDATA, HDATA, and CODE spaces. The SFR space is the only space that may not be accessed using the Universal Pointer mode.

The Universal Pointer addressing mode uses a new set of pointer registers for two reasons. The first is that 24-bit pointers are needed in order to allow addressing both the 8 MB code space and the 8 MB data space. The other reason is that it is much more efficient to manipulate multi-byte pointer values in registers than it is in SFRs. C compilers typically already perform pointer manipulation in registers, then move the result to a Data Pointer for use.

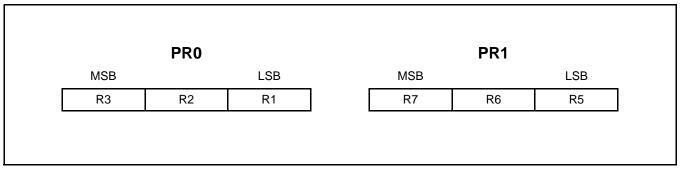

Two Universal Pointers are supported: PR0 and PR1. The pointer PR0 is composed of registers R1, R2, and R3 of the current register bank, while PR1 is composed of registers R5, R6, and R7 of the current register bank, as shown in Figure 14.

Figure 14: Universal Pointer Registers

51MX

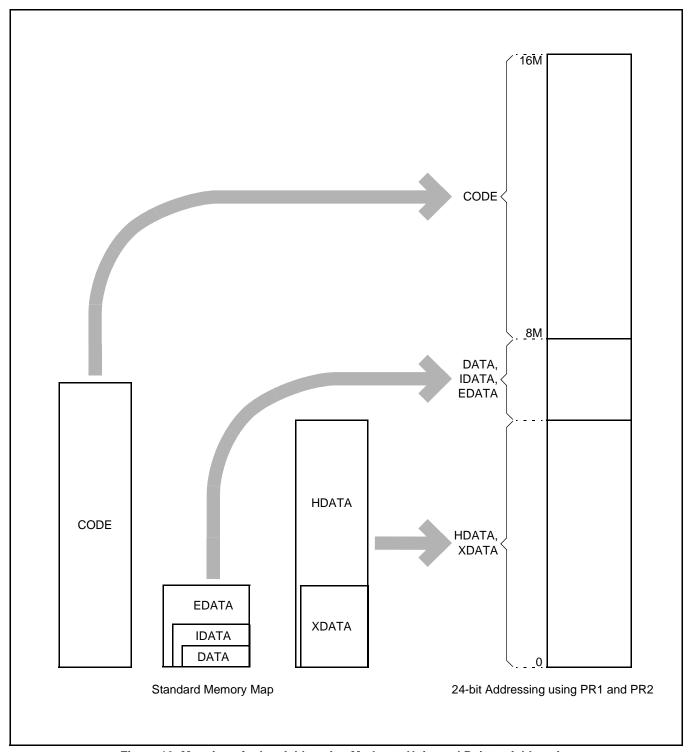

In order to access all of the various memory spaces in a single unified manner, they must all be mapped into a new "view" that allows 16 B of total memory space. This new view is called the Universal Memory Map.

The XDATA space is placed at the bottom of this new address map. The HDATA space continues above XDATA. The standard internal data memory spaces (DATA and IDATA) are above HDATA, followed by the remainder of the EDATA space. Finally, the code memory occupies the top of the map.

Thus, the most significant bit of the Universal Pointer determines whether code or data memory is accessed. By placing the XDATA space at the bottom of the Universal Memory Map, Universal Pointer addresses 00:0000 through 00:FFFF can correspond to the classic 80C51 external data memory space. This allows for full backward compatibility for code that does not need more than 64k of external data space. The Universal Memory Map is shown in Figure 15, while the standard view of the memory spaces and how they relate to Universal Pointer values are shown in Figure 16.

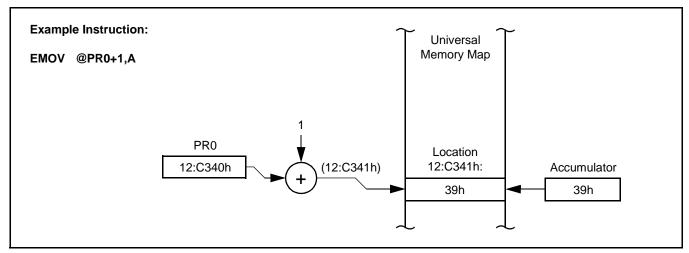

The Universal Pointers are used only by a new 51MX instruction called EMOV. The EMOV instruction allows moving data via one of the Universal Pointers into or out of the accumulator. In either case, a displacement of 0, 1, 2, or 3 may also be specified, which is added to the pointer prior to its use. The displacement allows C compiler access of variables of up to 4 bytes in size (e.g. Long Integers) without the need to alter the pointer value. An example of Universal Pointer usage is shown in Figure 17. Note that it is not possible to store a value to the CODE area of the Universal Memory Map.

Another new instruction is added to allow incrementing one of the Universal Pointers by a value from 1 to 4. This allows the pointer to be advanced past the last data element accessed, to the next data element.

Figure 15: Universal Memory Map

16

Figure 16: Mapping of other Addressing Modes to Universal Pointer Addressing

Figure 17: Memory Access using Universal Pointer Addressing

Universal Pointers are designed primarily to facilitate addressing in Extended Addressing Mode, with the EAM bit in MXCON set to one. However, Universal Pointers may still be used when EAM = 0. In this case, Universal Pointer addressing can access only the bottom 64 KB of the Code space, the 64 KB XDATA space, and the 64 KB EDATA space. The Universal Pointer values that point to these areas do not change. When EAM = 0, Universal Pointer accesses outside of these areas are not accessible and will return a value of FF hex.

# 3 INSTRUCTION SET OVERVIEW

The 51MX instruction set is a a true binary-level superset of the classic 80C51, designed to be fully compatible with previously written 80C51 code. The changes to the instruction set are all related to the expanded address space. Some details of existing instructions have been altered, and some instructions have had an extended mode added. In the latter case, the alternate mode of the instruction is activated by preceding the instruction with a special one-byte prefix code, A5h.

An important goal in the implementation of the 51MX was to keep the same timing relationship of existing 80C51 instructions to existing devices. Any 80C51 instruction executed on the 51MX will take the same number of machine cycles to execute.

Refer to Appendix A for details on 51MX instructions.

| 80C51 Instruction     | Effect of Extended Addressing                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All relative branches | Includes SJMP and all conditional branches. These instructions may cross a 64 KB boundary if they are located within branch range of the boundary.                                                                                                                                                                                                                                                                      |

| ACALL addr11          | This instruction will cross a 64 KB boundary if it is located such that the next instruction in sequence is across the boundary.                                                                                                                                                                                                                                                                                        |

| AJMP addr11           | This instruction will cross a 64 KB boundary if it is located such that the next instruction in sequence is across the boundary.                                                                                                                                                                                                                                                                                        |

| JMP @A+DPTR           | The lower 16-bits of the Program Counter are replaced with the value formed by the sum of the Accumulator and the active DPTR. This instruction will cross a 64 KB boundary if it is located such that the next instruction in sequence is across the boundary.                                                                                                                                                         |

| MOVC A,@A+DPTR        | The address formed by replacing the lower 16-bits of the Program Counter with the value formed by the sum of the Accumulator and the active DPTR is used to access code memory. The PC value used is that of the instruction following MOVC.                                                                                                                                                                            |

| MOVC A,@A+PC          | The sum of the Accumulator and the 23-bit Program Counter forms the 23-bit address used to read the code memory. The PC value used is that of the instruction following MOVC.                                                                                                                                                                                                                                           |

| MOVX @DPTR,A          | The active DPTR points to an address in the 64 KB XDATA memory.                                                                                                                                                                                                                                                                                                                                                         |

| MOVX A,@DPTR          | The active DPTR points to an address in the 64 KB XDATA memory.                                                                                                                                                                                                                                                                                                                                                         |

| RET                   | Replaces the lower 16 bits of the Program Counter with a 16-bit address from the Stack. This instruction will cross a 64 KB boundary if it is located such that the next instruction in sequence is across the boundary.                                                                                                                                                                                                |

| RETI                  | When the extended interrupt frame mode is not enabled, this instruction replaces the lower 16 bits of the Program Counter with a 16-bit address from the Stack. This will cause a 64 KB boundary to be crossed if the instruction is located such that the next instruction in sequence is across the boundary. If the extended interrupt frame mode is enabled, a 23-bit address is loaded into the PC from the stack. |

| LCALL addr16          | Replaces the lower 16 bits of the Program Counter with the 16-bit address. This instruction will cross a 64 KB boundary if it is located such that the next instruction in sequence is across the boundary.                                                                                                                                                                                                             |

| LJMP addr16           | Replaces the lower 16 bits of the Program Counter with the 16-bit address. This instruction will cross a 64 KB boundary if it is located such that the next instruction in sequence is across the boundary.                                                                                                                                                                                                             |

Table 1: Instructions Affected by Extended Address Space

| 80C51 Instruction |              | 51MX Effect<br>Without Prefix                                                                                                                               | 51MX Enhancement<br>(these instructions use<br>the prefix byte) |              | 51MX Effect with Prefix                                                                                                                                    |

|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCALL             | addr16       | Load a 16-bit address into the Program Counter.                                                                                                             | ECALL                                                           | . addr23     | Load a 23-bit address into the Program Counter.                                                                                                            |

| LJMP              | addr16       | Load a 16-bit address into the Program Counter.                                                                                                             | EJMP                                                            | addr23       | Load a 23-bit address into the Program Counter.                                                                                                            |

| JMP               | @A+DPTR      | The lower 16-bits of the Program Counter are replaced with the sum of the Accumulator and the active DPTR.                                                  | JMP                                                             | @A+EPTR      | The Program Counter is loaded with the value formed by the sum of the Accumulator and the EPTR.                                                            |

| MOVC              | A,@A+DPTR    | Code memory is accessed using the address formed by replacing the lower 16-bits of the Program Counter with the sum of the Accumulator and the active DPTR. | MOVC                                                            | A,@A+EPTR    | Code memory is accessed using the address formed by the sum of the Accumulator and the EPTR.                                                               |

| MOVX              | @DPTR,A      | The active DPTR points to an address in the 64 KB XDATA memory.                                                                                             | MOVX                                                            | @EPTR,A      | The EPTR points to an address anywhere in HDATA memory (not DATA, IDATA, or EDATA).                                                                        |

| MOVX              | A,@DPTR      | The active DPTR points to an address in the 64 KB XDATA memory.                                                                                             | MOVX                                                            | A,@EPTR      | The EPTR points to an address anywhere in HDATA memory (not DATA, IDATA, or EDATA).                                                                        |

| INC               | DPTR         | Increment the active Data Pointer.                                                                                                                          | INC                                                             | EPTR         | Increment the 23 bit EPTR.                                                                                                                                 |

| MOV               | DPTR,#data16 | Load a 16-bit value into the active Data Pointer.                                                                                                           | MOV                                                             | EPTR,#data23 | Load a 23-bit value into the EPTR.                                                                                                                         |

| RET               |              | Load a 16-bit address into the Program Counter from the Stack.                                                                                              | ERET                                                            |              | Load a 23-bit address into the Program Counter from the Stack.                                                                                             |

| ORL               | A,Rn         | Logically OR Register n to the Accumulator.                                                                                                                 | EMOV                                                            | A,@PRi+disp  | Load the Accumulator with the value from<br>the Universal Memory Map at the address<br>formed by PR0 or PR1plus the<br>displacement (a value from 0 to 3). |

| ANL               | A,Rn         | Logically AND Register n to the Accumulator.                                                                                                                | EMOV                                                            | @PRi+disp,A  | Load the Universal Memory Map address formed by PR0 or PR1 plus the displacement (a value from 0 to 3) with the contents of the Accumulator.               |

| XRL               | A,Rn         | Exclusive OR Register n to the Accumulator.                                                                                                                 | ADD                                                             | PRi,#data2   | Add an immediate data value from 1 to 4 to the specified Universal Pointer. This is a 24-bit addition.                                                     |

Table 2: Enhancements to the 80C51 Instruction Set Enabled by the Prefix Byte

# 4 INTERRUPT PROCESSING

Interrupt processing on the 51MX is the same as on the classic 80C51 but taking extended code addressing capability into account.

When an interrupt occurs, there are two possible actions, depending on the stack mode. If the stack is in 80C51 mode (EIFM=0 in MXCON sfr), the lower 16-bits of the Program Counter are saved on the stack. When the interrupt service routine completes, it returns to the interrupted code by executing the RETI (return from interrupt) instruction. This instruction loads the Program Counter with a 16-bit value, causing execution to resume at the point of interruption.

If the stack is in Extended Interrupt Frame Mode (EIFM=1 in MXCON sfr), the entire 23-bit Program Counter value is saved on the stack. The interrupt is still terminated by executing the RETI instruction. In the Extended Interrupt Frame Mode, this causes the entire 23-bit Program Counter to be loaded from the stack. In effect, the extended interrupt frame mode <u>must</u> be used if the program that can be interrupted extends beyond the 64 KB 80C51 limit.

## 4.1 INTERRUPT ENABLES AND PRIORITIES

The 51MX family uses four priority level interrupt structure. This allows great flexibility in controlling the handling of the many interrupt sources.

Each interrupt source can be individually enabled or disabled by setting or clearing a bit in dedicated registers. Global disable bit disables and enables all individually enabled interrupts at once.

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in interrupt priority registers. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. So, if two requests of different priority levels are received simultaneously, the request of higher priority level is serviced.

If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve simultaneous requests of the same priority level.

For more information on interrupt handling in an 51MX based device, please refer to the corresponding "User's Manual".

# 5 EXTERNAL BUS

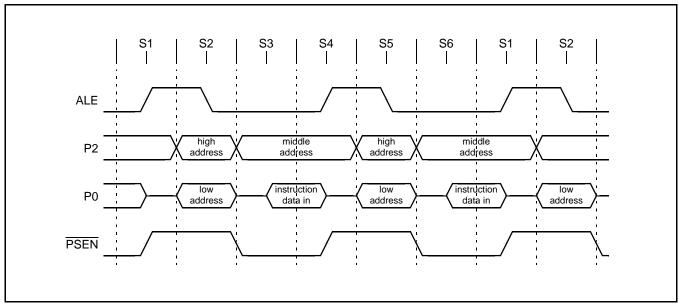

The external bus provides address information to external devices, and initiates code read, data read, or data write operations. In the 51MX devices, the external bus duplicates the classic 80C51 multiplexed external bus, but allows increasing the address output to 23 bits.

## 5.1 MULTIPLEXED EXTERNAL BUS

The 51MX external bus supports 8-bit data transfers and up to 23 address lines. The number of address lines available is configurable, and depends on the setting of the EAM in the MXCON register.

The default for an unprogrammed part following reset is 16 address bits. This provides drop-in compatibility in existing 80C51 sockets. A non-volatile configuration bit allows pre-selecting a 23-bit address size at the time that the part is programmed. Software may later enable the Extended Addressing Mode (by setting EAM=1 in MXCON sfr) even if the pre-programmed configuration does not. However, if non-volatile configuration bit is programmed and configures external bus to operate with 23 bits, this interface can not be reversed to 16 bits, characteristic for standard 80C51!

The non-volatile address configuration is implemented using EPROM technology. The configuration is comprised of a single bit that enables multiplexing of the 7 extended address bits on Port 2. If the non-volatile configuration bit is not programmed, extended addressing may be enabled at run time via the EAM bit in the MXCON SFR. Software may write a 1 to MXCON, changing the default configuration. Typically, this would be done a single time. If software reads the EAM bit in MXCON, the value will be the logical OR of the non-volatile configuration bit and the MXCON.EAM bit value. It is not recommended to change the address configuration dynamically during program execution (for example: changing EAM=1 to EAM=0 changes external memory bus interface and prevents core from executing code above the 64 KB boundary). The encoding of the configuration bit is such that an unprogrammed device is configured for 16 address lines. The erased state of the physical cell is interpreted in such a way as to produce that result.

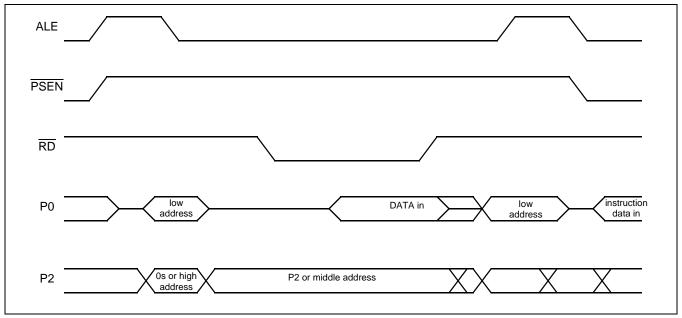

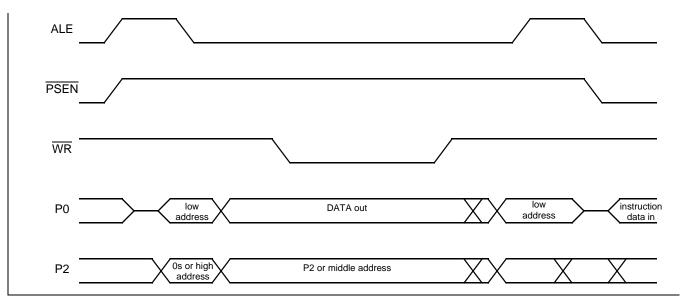

When the full 23-bit address is multiplexed on Port 2 (when the EAM bit in MXCON = 1), the high order address information (bits A22 through A16) must be latched externally in the same manner as the low order bits (A7 through A0) on Port 0. The middle address bits (A15 through A8) appear on Port 2 after ALE goes low. If extended addressing is not enabled, Port 2 behaves just as on a classic 80C51. An example of Port 2 address multiplexing is shown in Figure 18.

There are two special cases for Port 2 multiplexing when extended addressing is enabled: MOVX @Ri and MOVX @DPTR. These instructions do not supply a source for a full 23-bit external address. Where program memory is involved (jumps and MOVC), any "missing" address bits are supplied by the Program Counter (see Table 1). For MOVX, the additional bits are forced to zeroes to complete the address. So, MOVX @Ri will output a 23-bit address composed of seven zeroes for the upper address, Port 2 SFR contents for the middle byte of the address, and Ri contents for the bottom byte. Similarly, MOVX @DPTR will output a 23-bit address composed of seven zeroes for the upper address and the current DPTR contents for the middle and bottom bytes of the address. Figures 19 and 20 present signal waveforms when external DATA memory is accessed with all 23 address bits (EAM=1 in MXCON sfr).

In a single-chip application with code exceeding 64 KB (and thus having EAM=1) and need to preserve an old 80C51 bus interface, the instruction EMOV @PRi,A should be used instead of MOVX @Ri,A. By loading the content of P2 sfr to R3 and R2, execution of instruction EMOV @PR0,A will have exactly the same output in a system with EAM=1 as it is in case of MOVX @R0,A in a design with standard 80C51bus interface.

Some 51MX applications may use extended addressing and rely on software setting the EAM bit in MXCON (i.e. the non-volatile address configuration bit is not programmed). If such an application is set up in a way that the first code executed upon reset is off-chip, then the instruction that sets the EAM bit in MXCON must be located at or below address 00FBh. This is to prevent the external bus from supplying a 16-bit address when a 23-bit address is required. If the Program Counter were to reach address 0100h while EAM = 0, the apparent address (to external hardware that is expecting a 23-bit address) would become 01:0100.

Figure 18: Example of External Code Memory Read Cycles using 23 Address Bits

Figure 19: Example of External Data Memory Read Cycle using 23 Address Bits

Figure 20: Example of External Data Memory Write Cycle using 23 Address Bits

The standard control signals and their functions for the external bus are as follows:

| Signal name | <u>Function</u>                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE         | Address Latch Enable. This signal directs an external address latch to store the multiplexed portion of the address for the next bus operation. This may be either a data address or a code address.                                                                                                                                        |

| PSEN        | Program Store Enable. Indicates that the processor is reading code from the bus. Typically connected to the Output Enable pin of external EPROMs or other memory devices. External bus addresses for code memory may range from 00:0000 through 7F:FFFF. In the Universal Memory Map, these correspond to addresses 80:0000 through FF:FFFF |

| RD          | Read. The external data read strobe. Typically connected to the RD pin of external peripheral devices.                                                                                                                                                                                                                                      |

| WR          | Write. The write strobe for external data. Typically connected to the $\overline{\text{WR}}$ pin of external peripheral devices.                                                                                                                                                                                                            |

External bus addresses for data memory may range from 00:0000 through 7E:FFFF, which matches Universal Memory Map addresses. If on-chip XDATA is enabled, it will cause an addressing discontinuity in the external data address space. The DATA and IDATA spaces are always on-chip, and therefore always create such an addressing discontinuity.

# APPENDIX A 51MX INSTRUCTION SET

This section describes the 51MX instruction set. There is a definition of terms and notations used in this chapter and a summary of the whole instruction set (Table 1), followed by a detailed description of each instruction. The detailed description includes instruction encoding, byte count, timing, pseudocode equivalents, and examples for each instruction.

The 51MX instruction set is identical to the standard 80C51 instruction set with additions and extensions to allow extended addressing capabilities. These extensions are identified at the beginning of the description of each affected instruction type. The instruction set has been extended to allow branching anywhere within the extended 8 MB code address space, to allow using a new 23-bit pointer (EPTR) to access the 8 Megabyte data memory, and to provide a unified method of addressing the entire code and data space from a single 24-bit Universal Pointer.

## A.1 GLOSSARY OF TERMS AND NOTATION USED IN THIS SECTION

#### General:

@ Indicates an indirect reference (e.g.: @R0 refers to the memory address pointed to by the contents of R0).

: Used to divide a 23 or 24-bit address purely for visual clarity. For example 01:2345h.

A The Accumulator

AB The Accumulator and the B register, when both used as operands in the MUL and DIV instructions.

AC Auxiliary Carry flag from the PSW.

addr11 An 11-bit branch address used in ACALL and AJMP. The branch will be within the same 2 KB block of Code memory

as the first byte of the following instruction.

addr16 A 16-bit branch address used in LCALL and LJMP. The branch will be within the same 64 KB block of Code memory

as the first byte of the following instruction.

addr23 A 23-bit branch address used in ECALL and EJMP. The branch may be anywhere in the 8 MB Code memory.

B The B register.

bit The 8-bit address of an addressable bit in the internal data memory or in a Special Function Register.

/bit The logical complement (inverse) of an addressable bit.

C Carry flag from the PSW.

#data 8 bits of immediate data contained in the instruction.

#data2 2 bits of immediate data contained in the instruction.

#data16 16 bits of immediate data contained in the instruction.

#data23 23 bits of immediate data contained in the instruction.

direct An 8-bit immediate address contained in the instruction. This could be an internal data memory location (0-127) or

an SFR [i.e., I/O port, control register, status register, etc. (128-255)].

DPTR The active 16-bit Data Pointer. One of two Data Pointers, as selected by the Data Pointer Select bits.

EPTR The 23-bit Extended Pointer.

OV Overflow flag from the PSW.

PC The 23-bit Program Counter.

PR1 or PR0 of the currently selected Register Bank. Used in Universal Pointer addressing, PR1 is comprised of

R7:R6:R5 as a 24-bit entity. PR0 is comprised of R3:R2:R1 as a 24-bit entity.

rel An 8-bit signed relative displacement for branches, used by SJMP and all conditional jumps. Range is +127 to -128

bytes relative to first byte of the following instruction.

Ri R1 or R0 of the currently selected Register Bank. Used in indirect addressing.

Rn Any of registers R7 through R0 of the currently selected Register Bank.

SP The Stack Pointer.

#### **Pseudocode Notation:**

← Pseudocode assignment operator. Occasionally used as ↔ to indicate the interchange of data in both directions.

( ) Used to indicate "contents of" in the instruction operation pseudocode.

Examples: (R4) is the contents of register 4.

(C) is the contents of the Carry flag.

(N.x) Indicates bit x of object N.

(N.x-y) Indicates a range of bits from bit x to bit y of object N.

Example: (PC.15-8) is the contents of the Program Counter, bits 8 through 15.

AND Logical operation: bitwise AND.

OR Logical operation: bitwise OR.

XOR Logical operation: bitwise Exclusive-OR.

#### **Memory Spaces:**

DATA Lower 128 bytes of standard internal data memory space, accessed via direct addressing using instructions other than MOVX and MOVC. In pseudocode descriptions, the contents of a DATA location are shown as:

(DATA (direct))

IDATA Indirect Data. 256 bytes of internal data memory space, accessed via indirect addressing using instructions other than MOVX and MOVC. This area includes the DATA area and the 128 bytes immediately above it. In pseudocode descriptions, the contents of an IDATA location are shown as:

(IDATA (Ri))

EIDATA Extended Indirect Data. This space is an extension to the DATA and IDATA areas and allows up to a potential total of 64 KB). This area is accessed as Stack or via indirect addressing using Universal Pointers. In pseudocode descriptions, the contents of an EIDATA location are shown as:

(EIDATA (SP))

XDATA "External" Data. Up to 8,323,072 bytes (8 MB - 64 KB) of memory space addressed via the MOVX instruction. In pseudocode descriptions, the contents of an XDATA location is shown in one of the following forms:

( XDATA (Ri) ) ( XDATA (DPTR) ) ( XDATA (EPTR) )

CODE Up to 8 Megabytes of Code memory, accessed as part of program execution and via the MOVC instruction. In pseudocode descriptions, the contents of a CODE location is shown in one of the following forms:

```

( CODE ( (PC.22-16) : (A) + (DPTR) ) )

( CODE ( (A) + (PC) ) )

```

UMEM Universal Memory addressing mode that allows all of the other memory areas to be accessed through the use of a Universal Pointer. In pseudocode descriptions, the contents of a memory location addressed by a Universal Pointer are shown as:

( UMEM ( (PRi) + data2 ) )

### A.2 51MX INSTRUCTION SET SUMMARY

Table 1 contains a summary of the 51MX instruction set, with a brief description, byte count, and the number of oscillator periods required to execute each instruction. A detailed description of each instruction may be found in the section following the table.

| Mnemonic |                 | Description                                           | Bytes | Machine<br>Cycles |

|----------|-----------------|-------------------------------------------------------|-------|-------------------|

| Arithme  | etic Operations |                                                       |       |                   |

| ADD      | A,Rn            | Add register to Accumulator                           | 1     | 1                 |

| ADD      | A,direct        | Add direct byte to Accumulator                        | 2     | 1                 |

| ADD      | A,@Ri           | Add indirect RAM to Accumulator                       | 1     | 1                 |

| ADD      | A,#data         | Add immediate data to Accumulator                     | 2     | 1                 |

| ADD      | PRi,#data2      | Add immediate data to the specified Universal Pointer | 2     | 4                 |

| ADDC     | A,Rn            | Add register to Accumulator with Carry                | 1     | 1                 |

| ADDC     | A,direct        | Add direct byte to Accumulator with Carry             | 2     | 1                 |

| ADDC     | A,@Ri           | Add indirect RAM to Accumulator with Carry            | 1     | 1                 |

| ADDC     | A,#data         | Add immediate data to Accumulator with Carry          | 2     | 1                 |

| SUBB     | A,Rn            | Subtract Register from Accumulator with borrow        | 1     | 1                 |

| SUBB     | A,direct        | Subtract direct byte from Accumulator with borrow     | 2     | 1                 |

| SUBB     | A,@Ri           | Subtract indirect RAM from Accumulator with borrow    | 1     | 1                 |

| SUBB     | A,#data         | Subtract immediate data from Accumulator with borrow  | 2     | 1                 |

| INC      | A               | Increment Accumulator                                 | 1     | 1                 |

| INC      | Rn              | Increment register                                    | 1     | 1                 |

| INC      | direct          | Increment direct byte                                 | 2     | 1                 |

| INC      | @Ri             | Increment indirect RAM                                | 1     | 1                 |

| INC      | DPTR            | Increment the 16-bit DPTR                             | 1     | 2                 |

| INC      | EPTR            | Increment the extended 23-bit EPTR                    | 2     | 2                 |

| DEC      | A               | Decrement Accumulator                                 | 1     | 1                 |

| DEC      | Rn              | Decrement Register                                    | 1     | 1                 |

| DEC      | direct          | Decrement direct byte                                 | 2     | 1                 |

| DEC      | @Ri             | Decrement indirect RAM                                | 1     | 1                 |

| MUL      | AB              | Multiply A and B                                      | 1     | 4                 |

| DIV      | AB              | Divide A by B                                         | 1     | 4                 |